Der Artikel wurde auf der Grundlage meiner eigenen Erfahrung mit Versuchen erstellt, dieses Thema mir, Studenten-Auszubildenden und neugierigen Kollegen zu erklären, um nicht in den abstrusen akademischen Dschungel einzutauchen, sondern so einfach und transparent wie möglich in der Alltagssprache. Ich habe gelernt, mit FPGAs zu arbeiten, ohne dieses Thema zu studieren und zu trainieren, und ich weiß aus eigener Erfahrung, wie schwierig es ist, etwas ohne theoretische Grundlage in diesem Thema und in Schaltkreisen zu verstehen. Für einen erfahrenen Züchter ist das oben Genannte elementar. Aber für einige Schüler im vierten Jahr wird der Artikel nützlich sein und helfen, all diese Lücken, Einstellungen und Griffe zu verstehen.

In dem Artikel werde ich Begriffe verwenden, deren englische Version in Klammern angegeben ist. Dies geschieht, weil eine einheitliche Terminologie nicht festgelegt ist und es bei der Vervielfältigung einfacher ist, zu verstehen, welches Konzept diskutiert wird, und gegebenenfalls Informationen darüber in englischsprachigen Quellen zu finden.

Einführung

Ich werde eine kurze Einführung in die Sprache einfacher Konzepte geben.

Damit etwas im FPGA funktioniert, müssen Sie die Firmware-Datei mit dem Programmierer und dem Firmware-Dienstprogramm laden (hochladen, nähen). Die Firmware-Datei ist das Produkt einer CAD-Zusammenstellung eines bestimmten Projekts - Ordner mit Dateien, von denen jede einen bestimmten Aspekt des Projekts beschreibt. In einfachen Fällen beschreibt der Benutzer selbst nur Dateien mit Quellcode, eine Datei mit Pinbelegung und eine Datei mit zeitlichen Einschränkungen. Der Rest der Dateien wird leise von CAD verarbeitet. Von dieser Triade ist nur die Zeitbeschränkungsdatei formal optional.Teil des Projekts. Wenn Ihr Projekt keine Frequenzen über 30-50 MHz enthält, ist es wahrscheinlich, dass es ohne diese Datei irgendwie funktionieren kann. Diese Option eignet sich für die einfache Erstellung der ersten Bildungsprojekte. Wenn Ihr Schulungsprojekt jedoch bereits hohe Taktfrequenzen enthält und nicht mit einer Zeitbeschränkungsdatei ausgestattet ist, wird die Datenverarbeitung wahrscheinlich irgendwo im FPGA unterbrochen, und Sie können nicht herausfinden, zu welchem Zeitpunkt im Projekt. Für Arbeiten, nicht für Studien, ist die Beschreibung der vollständigen Beschränkungsdatei unbedingt erforderlich . Es liegt in Ihrer Verantwortung, die Funktionalität Ihres Projekts zu überprüfen und zu validieren.

Der Compiler platziert Ihr Projekt auf dem FPGA-Chip und empfängt eine Datei mit Verbindungen aller physischen Elemente. Der Timing-Analysator berechnet anhand der Verbindungsdatei die Dauer der Datenübertragung zum FPGA. Diese Dauer sollte nicht unendlich lang oder zu kurz sein. Die Datei mit den Zeitbeschränkungen teilt dem Analysator mit, in welchem Rahmen diese Dauer sein soll. Anhand der Ergebnisse der Zeitanalyse kann der Entwickler erkennen, in welchen Teilen des Projekts ein Zeit- und damit ein Frequenzspielraum besteht und wo es keinen solchen Spielraum gibt.

Synchrone Systeme synchronisieren die Datenverarbeitungsarbeit mit Synchronisationstaktsignalen, die im Jargon kurz als Uhren der englischen Uhr bezeichnet werden... Zwischenergebnisse von Operationen werden in Registern gespeichert, die den Zustand am Eingang zum Zeitpunkt des Eintreffens der Taktsignalflanke speichern und bis zum nächsten Taktzyklus am Ausgang halten können.

Somit bestehen Synchronschaltungen aus Interregister-Datenübertragungen ( RTL, Registerübertragungslogik, r2r-Übertragung ). Ein wesentlicher Aspekt der zeitlichen Analyse besteht in der Messung von Slack ( Slack ). Dieses Wort bedeutet wörtlich übersetzt "Zeitreserve", "Absacken", aber im russischsprachigen Umfeld wird häufig Transparentpapier aus dem Englischen verwendet - "schlaff". Bei Interregister-Übertragungen handelt es sich um voreingestellte Slacks ( Setup ) und Hold Slacks ( Hold ).

Übertragung zwischen Registern

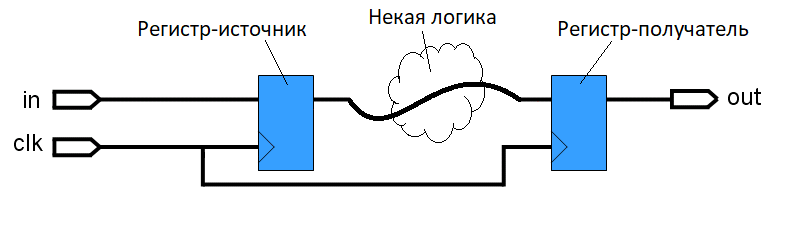

Die Übertragung zwischen Registern (Fig. 1) wird als ein System von zwei nacheinander verbundenen Registern betrachtet, die im allgemeinen Fall mit synchronen Takten arbeiten. Im einfachen Fall auf einem Stück. Ein Register spielt die Rolle der Quelle (Quelle) und die andere Rolle des Datenempfängers (Ziel). Und bei der nächsten Übertragung zwischen Registern wird dieses Empfangsregister bereits als Quelle usw. betrachtet. Zwischen den Registern auf dem Datenpfad befindet sich eine beliebige benutzerdefinierte Kombinationslogik. Es ist asynchron, da es keine Speicherelemente mit einem Synchronisationssignal wie Register enthält. Diese Logik ist das Verhalten, die logischen Operationen, die der Benutzer mit seinem Code beschreibt. Register sind die Ein-Bit- "Variablen", denen der Benutzer im Code Namen gibt und die separat arbeiten.oder Kombinieren zu Vektoren und Arrays.

Zahl: 1. Schema der Datenübertragung von Register zu Register

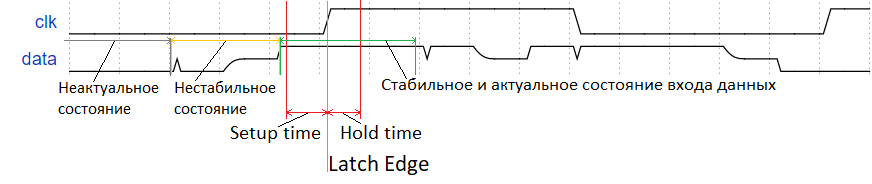

Mit dem Empfang von Daten durch das Empfangsregister sind zwei Konzepte verbunden: Rüstzeit und Haltezeit. Sie beschreiben den Zeitraum, in dem das Signal am Eingang des Empfängers stabil und relevant sein muss. Stabil - bedeutet im Wesentlichen, dass seine Spannung sehr nahe an einem von zwei logischen Zuständen liegen sollte - "0" oder "1" - und nicht mit der Wahrscheinlichkeit von Verwechslungen zwischen ihnen baumeln sollte. Relevant - bedeutet, dass sich dieses Informationsbit in seiner Bedeutung auf diesen Takt der Uhr beziehen sollte, der es erfasst, und nicht auf ein spätes Bit des vorherigen Takts.

Rüstzeit - voreingestellte Zeit, die Mindestzeit, für die das Datensignal vor dem Eintreffen der Taktfront bereits in einem stabilen Zustand hergestellt werden sollte.

Haltezeit - die Haltezeit, die Mindestzeit , die noch nach der Ankunft der Uhr Front, muss das Datensignal in einem stabilen Zustand gehalten werden.

Das heißt, die Daten am Eingang des Empfängers müssen nicht nur zum Zeitpunkt des Eintreffens der Uhrfront, sondern auch während eines bestimmten Schutzzeitintervalls (Abb. 2) mit einer Dauer von mindestens Setup_time + Hold_time stabil und aktuell sein. Wenn die Datenstabilitätsbedingung während dieses Intervalls erfüllt ist, kann das Register die eingehenden Daten definitiv fehlerfrei erfassen, andernfalls garantiert niemand, dass kein Fehler auftritt.

Zahl: 2.Einrichtungszeit und Haltezeit als Schutzintervall um die Erfassungsflanke am Takteingang des Registers

Die Werte für Setup-Zeit und Haltezeit werden vom FPGA-Hersteller streng definiert. Sie hängen von der Kristallherstellungstechnologie ab und gelten als Konstanten für die Analyse, die für jedes Register im Kristall gleich sind. In jedem Fall hängen diese Werte in keiner Weise vom Benutzer ab, ihre Abrechnung ist nur eine Aufgabe für das Zeitanalyse-Dienstprogramm. Es ist nicht wichtig für uns zu wissen, was sie gleich sind, es ist wichtig für uns nur zu wissen, dass sie existieren und nicht gleich Null sind.

Die Essenz der Zeitanalyse besteht darin, die Lücken für jedes Registerpaar im Projekt zu berechnen, zwischen denen eine Datenübertragung stattfindet, damit die Daten während des Schutzintervalls stabil sind. Es gibt viele solcher r2r-Paare im Projekt, Tausende oder sogar Millionen, aber jedes von ihnen muss analysiert werden, um sicherzustellen, dass das Projekt funktioniert.

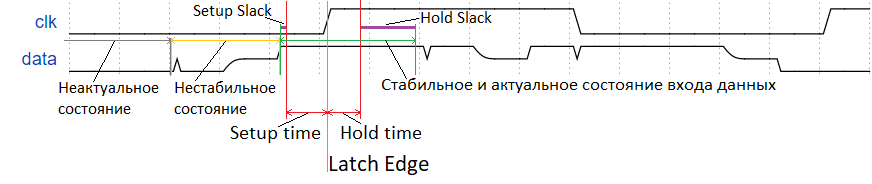

Es gibt auch zwei Durchhänge - Setup Slack und Hold Slack (Abb. 3).

Setup Slack kennzeichnet die Zeitspanne, die die Daten vom Zeitpunkt der Stabilisierung bis zum Beginn des Setup-Zeitintervalls haben.

Hold Slack kennzeichnet die Zeitspanne, die Daten vom Ende des Hold-Zeitintervalls bis zum Stabilitätsverlust der Daten haben.

Die Hosen müssen positiv sein. Wenn der Durchhang negativ ist, ist die Stabilitätsbedingung der Eingabedaten nicht erfüllt und die Daten schlagen. Je lockerer - desto besser, aber Sie müssen verstehen, dass bei jedem Registerziel die voreingestellten und gehaltenen Lücken eine gemeinsame Zeit für zwei haben. Dies bedeutet, dass eine Zunahme eines Durchhangs immer zu einer Abnahme des anderen führt. Daher ist die beste Option, wenn beide Durchhänge positiv und ungefähr gleich sind, d.h. Das Gleichgewicht der Durchhänge wird beobachtet.

Zahl: 3. Positive Slacks, die Voraussetzung für einen erfolgreichen Datenempfang ist erfüllt, es besteht jedoch kein Gleichgewicht zwischen den Slacks

Durchhangberechnung

Fahren wir nun mit der Berechnung dieser Durchbrüche fort. Beginnen wir mit Setup Slack.

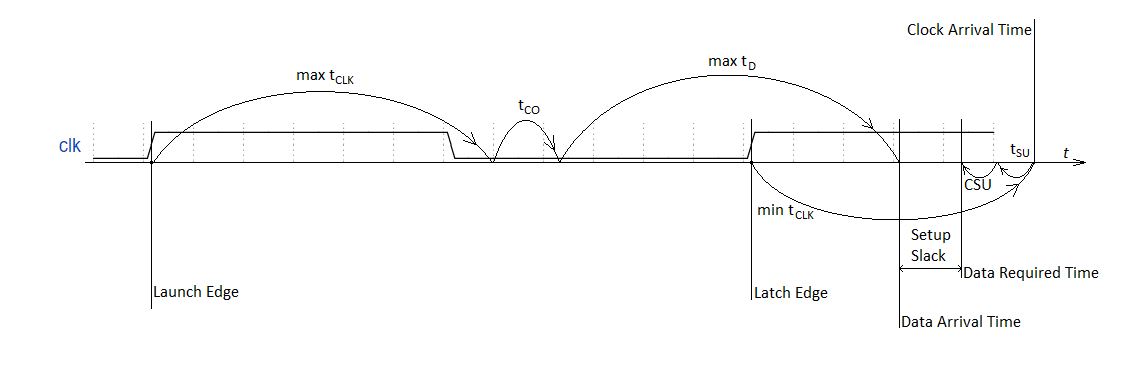

Betrachten Sie das Datenübertragungsschema in Abb. 4.

Abb. 4. Datenübertragungsschema

Hier stellen wir Konzepte wie Triggerfront, Erfassungsfront, Datenankunftszeit, Datenwartezeit und Uhrankunftszeit vor.

Die Startkante ist die Vorderseite der Uhr, die an den Eingang des Quellregisters gelangt ist und den Datenübertragungsprozess gestartet hat.

Die Latch Edge ist die Taktfront, die am Empfangsregister ankommt und es zwingt, Daten bei der Eingabe zu erfassen.

Der Zeitpunkt des Eintreffens von Daten ( Datenankunftszeit ) ist definiert als der tatsächliche Eintreffen von Daten im Empfangsregister.

Die erforderliche Datenzeit ist definiert als die Zeit, die Daten benötigen, um das Ziel vor der voreingestellten Zeit im Zielregister zu erreichen.

Die Ankunftszeit einer Uhr ( Clock Arrival Time ) ist definiert als die Zeit des Durchgangs der Flanke der Erfassung vom Takteingang der gesamten Schaltung zum Takteingang des Empfängers. Darüber hinaus bedeutet die Erfassungsfront die nächste Front nach der Startfront. Die Startfront sendet Daten von der Quelle an den Empfänger, und nach einer Taktperiode erfasst die Erfassungsfront diese Daten auf der Empfängerseite.

Der Takteingang der gesamten Schaltung wird als ein einzelner Punkt verstanden, von dem der Takt zu allen daran arbeitenden Registern abweicht. Dies ist normalerweise die Ausgabe des globalen Taktpuffers oder die Ausgabe der PLL. Im primitivsten Fall ist dies der FPGA-Zweig, an den der Taktgenerator angeschlossen ist.

Die an der zeitlichen Analyse beteiligten Begriffe haben möglicherweise keinen Punktwert, sondern einen bestimmten Bereich möglicher Werte, abhängig von der Entwurfsspur und der Kristalltemperatur. Daher wird der schlechteste Durchhang analysiert. Der Datenaustausch gilt als erfolgreich, wenn er auch unter den schlechtesten Bedingungen für einen Durchhang positiv bleibt.

In welcher Beziehung steht der Moment des Datenankunfts zur Triggerflanke?

Wir betrachten das Eintreffen von Daten als Durchlaufen einer Kette mit einem Register eines Ereignisses, das durch eine Triggerflanke ausgelöst wird.

Die Startflanke erscheint am Takteingang des Systems, erreicht dann für einige Zeit den Eingang des Quellregisters, dann wird dieses Register für einige Zeit ausgelöst und sendet neue Daten an den Ausgang, dann werden diese Daten durch die kombinatorischen Logikschaltungen zum Empfangsregister geleitet. Die schlechteste und langsamste Variante der Datenübertragung wird berücksichtigt, daher werden die Begriffe mit dem Präfix "max" versehen.

In dieser Formel hat der Begriff für die Triggerflanke die Bedeutung eines Referenzpunkts, relativ zu dem sich Ereignisse entwickeln, und nicht eines in Nanosekunden gemessenen Wertes.

BegriffIst die maximale Zeit, die die Triggerflanke benötigt, um vom Takteingang der gesamten Schaltung zum Takteingang der Quelle zu gelangen. In der Regel nimmt der Analysator einfach den Zeitbereich von „genau nicht weniger als“ bis „genau nicht mehr als“ und setzt die Obergrenze „definitiv nicht mehr als“ in diese Formel ein. Dieser Wert ist unabhängig vom Benutzer. Der Compiler entscheidet selbst, wo das Register auf dem Kristall platziert werden soll, und berücksichtigt die Zeit, die die Uhr benötigt, um dorthin zu gelangen. Das Netzwerk von Verbindungen, über das das Taktsignal vom globalen Taktpuffer zu Registern abweicht, ist so ausgelegt, dass das Taktsignal in nahezu derselben Zeit jedes Register erreicht. Daher ist in der Tat der Unterschied zwischen und extrem klein, aber immer noch berücksichtigt.

Begriff- Dies ist die Zeit von Takt zu Ausgang , die das Register verbringt, um zu sehen, wie die Flanke am Takteingang die Daten an seinem Ausgang ändert. Der Analysator betrachtet diesen Wert für alle Register auf dem Chip als gleich. Dieser Wert ist unabhängig vom Benutzer.

Die letzte AmtszeitIst die maximale Zeit, die ein Ereignis (Daten) benötigt, um die vom Benutzer definierte Kombinationslogik zwischen Registern zu durchlaufen. Dieser Wert ist stark vom Benutzer abhängig. Es drückt den Umfang der kombinatorischen Logik zwischen Registern aus. Lange Ketten kombinatorischer Logik sind wiederum häufig das Ergebnis einer ungenauen Codierung durch den Benutzer.

Der Moment, in dem der Shred beim Empfänger eintrifft, ist einfacher zu berechnen:

Dies ist der früheste Zeitpunkt, zu dem die Erfassungsflanke den Takteingang des Empfangsregisters erreicht.

Begriff- Dies ist die Mindestzeit, für die die Erfassungsfront den Takteingang des Empfängers erreicht, dh in Analogie zur vorherigen Formel beträgt diese Zeit „definitiv nicht weniger als“. Der Strich bedeutet in diesem Fall, dass es sich um den Takteingang des Empfängers handelt, nicht um die Quelle.

Die Wartezeit für Daten ist definiert als die Zeit, die Daten benötigen, um den Empfänger vor der voreingestellten Zeit im Empfängerregister zu erreichen:

Begriff - Dies ist uns bereits bekannt. Die Einrichtungszeit wird für jedes Register auf dem Kristall als gleich angesehen. Diese Zeit ist unabhängig vom Benutzer.

BegriffIst die Einstellung der Uhr unsicher , voreingestellte Zeitunsicherheit. Wie jede andere Unsicherheit bei der zeitlichen Analyse einer CSU ist dies kein physikalischer Prozess, sondern eine Möglichkeit, den Einfluss von Jitter in der Analyse widerzuspiegeln, oder einfach eine Möglichkeit, für alle Fälle eine Schutzzeit in die Analyse einzuführen. Mit einfachen Worten, dies ist eine Zeitreserve, um schwierige Prozesse zu berücksichtigen.

Nachdem diese Begriffe definiert wurden, können wir einen voreingestellten Durchhang als den kleinsten Unterschied zwischen der Zeit, die zum Ziel reisen darf, und der Zeit, die tatsächlich benötigt wird, definieren.

Erweitern wir nun diese Begriffe und ordnen sie ein wenig neu an:

Hier sind neue Begriffe erschienen.

Es ist klar über die Periode, dies ist die Periode der Taktfrequenz, d.h. Zeit zwischen Launch Edge und Latch Edge.

Begriff- Dies ist der Taktversatz - Der Minimalwert der Streuung der Ankunftszeit einer Taktfront vom Takteingang des Systems auf verschiedene Synchronregister. Die minimale Taktspreizung ist definiert als die Differenz zwischen der kleinsten Taktverzögerung zum Empfänger und der größten Taktverzögerung zur Quelle.... Der Analysator macht keinen Unterschied bei der Schätzung dieser Zeit für verschiedene Register auf dem Chip.

So haben wir den voreingestellten Durchhang berechnet. Eine positive Marge ist gut, eine negative Marge ist schlecht. Schlaffheit bedeutet wörtlich Durchhängen. Wenn also ein Durchhang vorliegt, ist die Interregister-Übertragung nicht als "vnatyag" konfiguriert, der bedingte "Thread" hängt frei ab. Durchhang ist negativ - dies bedeutet, dass das Getriebegewinde überzogen und gebrochen wurde.

Abbildung 5 zeigt, wie die Slack-Formel grafisch dargestellt werden kann:

Abb. 5. Grafische Darstellung des Setup Slack-Ausdrucks

Dies zeigt die Beziehung im Hintergrund des Taktsignals. Dies ist das Taktsignal am Takteingang des Systems und nicht am Eingang eines der Register.

Berechnen wir nun den Retentionsspielraum auf ähnliche Weise .

Es kann auch durch einen Ausdruck dargestellt werden, in dem die Begriffe Vorzeichen geändert haben:

Diese Begriffe werden nun von der anderen Seite betrachtet.

Nun wird hier die schnellste Variante der Datenübertragung betrachtet und wobei "max" "min" war.

Der Moment der Ankunft der Clok-Front wird auch in einer anderen Richtung gesehen, als der spätestmögliche:

Es ist wichtig zu beachten, dass im Fall von Hold Slack die Fronten Launch Edge und Latch Edge jetzt dieselbe Front sind und nicht mehr zwei verschiedene Fronten, die durch die Taktperiode getrennt sind. In dieser Situation muss das Empfängerregister Zeit haben, um die Daten während der Haltezeit ab dem Eintreffen der Taktfront am Eingang zu halten. Die Daten werden jedoch an ihrer Eingabe von derselben Front geändert, die an einer anderen Stelle in das Quellregister gelangt ist. Daher ist bei der Analyse des Retentionsspiels der Unterschiedgleich Null, nicht die Periode.

Die erforderliche Zeit ist in diesem Fall definiert als die Zeit, während der sich die Daten bei der Eingabe der Daten des Empfängers nicht ändern sollten, um die Haltezeit nicht zu erfassen:

Begriff - das ist uns schon bekannt Haltezeit, Haltezeit. Es wird für jedes Register auf dem Chip als gleich angesehen und hängt nicht vom Benutzer ab.

BegriffIst Clock Hold Unsicherheit , ist die Unsicherheit der Haltezeit. Es hat im Allgemeinen die gleiche Bedeutung wie CSU und wird in der Regel gleichgesetzt.

Wenn Sie wie im Fall des voreingestellten Slacks die Begriffe erweitern und austauschen, kann der Ausdruck für den Retention Slack in die folgende Form umgewandelt werden:

Ein weiterer Blick auf diese Formel

Oben wurde eine Methode zur Berechnung des Durchhangs vorgestellt, die für das menschliche Verständnis der ablaufenden Prozesse charakteristisch ist. Hier "kommt die Front ...", "Daten kommen ...". Wenn Sie interessiert sind, werde ich Ihnen als Ergänzung erklären, wie sich der Analysator von Zeitbeschränkungen diese Berechnungen vorstellt.

Der Analysator gruppiert die Begriffe je nach Maschinengründen unterschiedlich. Aber am Ende kommt es zum gleichen Ergebnis.

Es werden die Begriffe Clock Setup Relationship ( SR ) und Clock Hold Relationship ( HR ) verwendet, die als Verhältnis der Zeit zwischen den Triggerflanken für Preset bzw. Hold übersetzt werden können.

Abbildung 6 zeigt, wie diese Fronten zusammenhängen:

Abb. 6. Fronten, die bei Durchhangberechnungen verwendet werden.

Sie können die resultierenden Ausdrücke sofort in eine verständlichere Form konvertieren:

Die längste Zeit zwischen den Registern (Größter r2r erforderlich) ist die maximale Zeit, die Daten zur Verfügung stehen, um das Ziel vor dem Beginn des voreingestellten Intervalls zu erreichen:

Die längste Verzögerung zwischen den Registern (längste r2r-Verzögerung) ist die Zeit, die benötigt wird, um Daten auf dem längsten Pfad vom Quellregister zum Zielregister zu übertragen:

Wir können nun den voreingestellten Durchhang als die Differenz zwischen der verfügbaren Zeit zum Erreichen des Zielregisters und der tatsächlichen Zeit zum Erreichen dieses Ziels definieren:

Wenn Sie die Begriffe dieser Formel erweitern, erhalten Sie die vertraute Darstellung des voreingestellten Durchhangs:

Nun zum Retentionsspiel. Die kleinste r2r-Anforderung ist die Zeit, die benötigt wird, um Daten am Eingang des Zielregisters zu halten:

Kürzeste Verzögerung zwischen den Registern:

Jetzt definieren wir den Durchhang der Voreinstellung als die Differenz zwischen der schnellsten Zeit, in der Daten den Eingang des Empfängers verlassen, und der Zeit, die erforderlich ist, um sie dort zu halten:

Bei der Erweiterung der Begriffe nimmt der Ausdruck auch die bereits bekannte Form an:

Welche Schlussfolgerungen können aus langweiligen Formeln gezogen werden?

Wir haben gesehen, wie Schlupf berechnet wird. Wie kann man dieses Wissen nutzen?

Schauen wir uns noch einmal die lockeren Ausdrücke an:

Wenn einige Lücken des Projekts negativ wurden, können wir sie ändern, indem wir ihre Bedingungen ändern. Das heißt, wir sehen, wie wir schlechte Hosen reparieren können.

Wir sehen Begriffe, die nicht vom Benutzer abhängen, sondern nur von der Kristalltechnologie. Das... Es gibt keine Möglichkeit, sich einzumischen.

Wir sehen die CSU- und CHU-Terme, die der Analysator normalerweise gleich dem CU-Parameter nimmt - Taktunsicherheit, Taktfrequenzinstabilität. Im Allgemeinen ist dieser Parameter klein, zehn Pikosekunden. Sie wird vom Benutzer in der Einschränkungsdatei angegeben. Und der Benutzer nimmt es wiederum aus der Spezifikation für den Taktgenerator. Es wird angenommen, dass ein Taktpuffer oder eine interne FPGA-PLL, die einen externen Takt vom Oszillator empfängt und ihn am Systemtakteingang in einen internen Takt umwandelt, den CU-Wert auf dem gleichen Wert hält wie den vom Oszillator empfangenen. Wenn keine CU angegeben ist, setzt der Analysator einen Standardwert, z. B. setzt Quartus ihn auf 20 ps. Im allgemeinen Fall sagt uns dieser Begriff, dass es besser ist, hochstabile Oszillatoren mit einer geringen Instabilität für die Taktung zu verwenden. Gute Oszillatoren liegen in der Größenordnung von 20 bis 60 ps.

Der Zeitraum zeigt, dass der offensichtliche Weg zur Bekämpfung der Fehlleitung der Datenübertragung darin besteht, die Taktfrequenz zu verringern. Dies ist vernünftig, aber nicht immer akzeptabel, da die Leistungsbeschreibung normalerweise eine gewisse Systemleistung erfordert, unter die Sie nicht gehen können. Und die Leistung hängt direkt von der Taktrate ab. Wir können auch den Unterschied zwischen dem voreingestellten und dem Hold-Slack erkennen - der Hold-Slack ist unabhängig von der Frequenz.

Und schließlich der Begriffcharakterisiert im Wesentlichen die Effizienz des geschriebenen Codes. Daher besteht der Hauptweg zur Lösung von Durchhangproblemen darin, sie richtig umzuschreiben. Große Zeiterscheint in zu komplexen Hardware-Designs, die zu viel kombinatorische Logik erfordern. Wenn Sie so komplexe Konstruktionen in Ihrem Projekt haben, besteht die klassische Methode zur Lösung des Problems darin, eine komplexe r2r-Übertragung in mehrere einfache zu teilen und der Abfolge der Operationen 1-2 weitere Register hinzuzufügen. In diesem Fall erhöht sich die Verzögerung der Zyklen für den Betrieb, aber die Betriebsgeschwindigkeit erhöht sich. Zum Beispiel ist das Hinzufügen mehrerer Vektoren in einem Taktzyklus keine gute Idee. Es ist besser, mehrere Vektoren nacheinander mit Zwischensummen zu addieren. Es kann unmöglich sein, einige komplexe Konstruktionen in eine Pipeline von mehreren einfachen zu zerlegen - dann muss eine solche Logik auf eine grundlegend andere Weise umgeschrieben werden.

Fazit

In diesem Artikel geht es darum, etwas über die Existenz des Konzepts eines Durchhangs und darüber zu erfahren, wovon dieser Durchhang physikalisch abhängt. Wenn Sie dies wissen, können Sie die Berichte des Analysators über Zeitbeschränkungen unabhängig studieren, Schlussfolgerungen ziehen und die Leistung Ihres Projekts debuggen. Dies sind Formeln, nach denen Sie kaum jemals eine echte Berechnung durchführen müssen. Sie müssen sich nicht einmal auswendig an sie erinnern. Es ist nur wichtig, die Logik des Interregister-Transfers zu verstehen und zu verstehen, welche Faktoren die Geschwindigkeit des Projekts bestimmen.