Zuletzt bin ich auf eine der Optionen für ein Debug-Board mit SoC Zynq XC7Z020 gestoßen. Nachdem ich im Internet nach Materialien gesucht und versucht hatte, mein Minimalprojekt einzubringen, stellte ich fest, dass es eine Reihe von Fallstricken gibt. Darüber möchte ich im Artikel sprechen. Wen kümmert es - willkommen bei Katze.

Wichtig! Bevor ich mit der Geschichte beginne, möchte ich im Voraus reservieren, dass das Hauptziel, das ich beim Schreiben dieses Artikels verfolge, darin besteht, Amateuren zu zeigen, wo sie anfangen sollen, wenn sie Zynq-basierte Debug-Boards studieren. Ich bin kein professioneller Entwickler für FPGA und SoC Zynq und kann Fehler bei der Verwendung der Terminologie machen, nicht die optimalsten Methoden zur Lösung von Problemen verwenden usw. Aber jede konstruktive und gut begründete Kritik ist nur willkommen. Also, lasst uns gehen ...

Was für ein Debugging ist das? Show-Tell ...

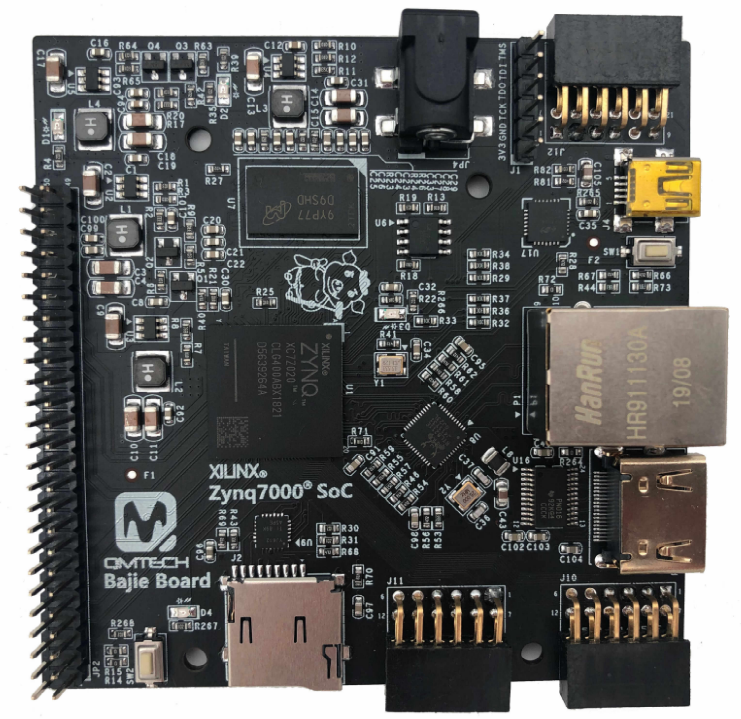

Ich wollte sehr lange mit SoC Zynq spielen, aber meine Hände konnten nicht erreichen. Aber noch einmal googeln - ich habe gesehen, dass das Debuggen mit Zynq an Bord von QMTech zu einem völlig vernünftigen Preis verkauft wird, es heißt Bajie Board. Debug ist in verschiedenen Varianten mit verschiedenen Zynq SoC-Varianten erhältlich. Ich habe mir die XC7Z020-Version ausgesucht und sie sofort bestellt, nach ein paar Wochen hatte ich sie bereits in der Hand.

, . , 5/2, mini-USB microSD Flash- SanDisk 16 Linux. , , USB-, Putty mini- Embedded Linux. Linux Zynq, , , ...

, -:

SoC: XC7Z020-1CLG400C

(datasheet:https://www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf);

33,333 ;

DDR3 512 Micron, MT41K256M16TW-107:P;

micro SD;

FPGA TPS563201 ( 4.5V 17V, 3A);

50- Digilent PMOD , , 2,54 . ( , );

(PS);

RGMII Ethernet- Realtek RTL8211E-VL, PS;

, (PL) (PS);

HDMI- TI TPD12S016;

JTAG-;

.

, , - JTAG-. .

, Xilinx Vivado Xilinx SDK. , , Vivado . Xilinx SDK ( Vitis) .

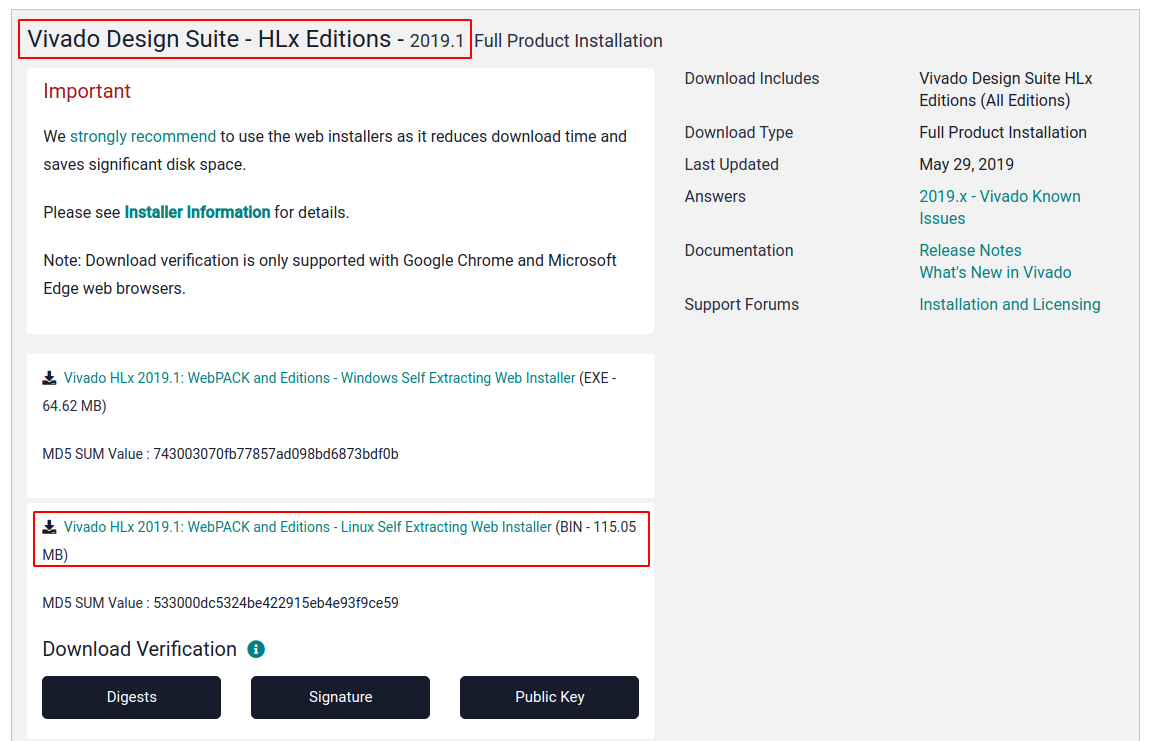

YouTube Vivado 2019.1 ( - , Xilinx SDK) - , 2020.2.

Xilinx Zynq - Xilinx, . , , Vivado - 2020.2, 2020.3 .. Versal SoC, Zynq.

, .. Linux - Vivado Archive - 2019.1 Vivado HLx 2019.1: WebPACK and Editions - Linux Self Extracting Web Installer Vivado Design Suite - HLx Editions - 2019.1. Windows - Windows Self Extracting Web Installer.

, :

chmod +x ~/Downloads/Xilinx_Vivado_SDK_Web_2019.1_0524_1430_Lin64.bin ~/Downloads/Xilinx_Vivado_SDK_Web_2019.1_0524_1430_Lin64.bin

.

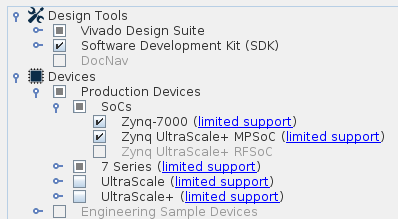

, ;

;

Vivado HL WebPACK;

, SoC Zynq .

16 -, .

Vivado JTAG-. Linux :

cd Xilinx2019.1/Vivado/2019.1/data/xicom/cable_drivers/lin64/install_script/install_drivers/

sudo ./install_drivers

6 JTAG- . :

cd ~/Xilinx2019.1/Vivado/2019.1/bin

./xsdb

xsdb% connect -host localhost

xsdb% jtag targets

1 Platform Cable USB 13724327082b01

2 arm_dap (idcode 4ba00477 irlen 4)

3 xc7z020 (idcode 23727093 irlen 6 fpga)

.

Hello, world “ ”

LED- .

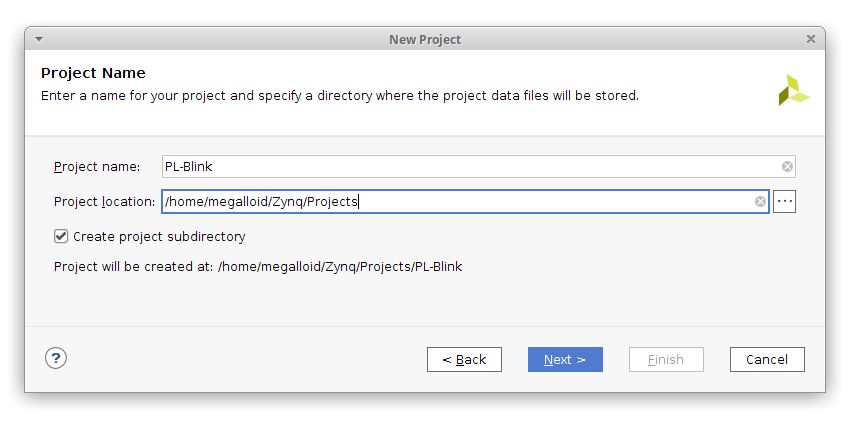

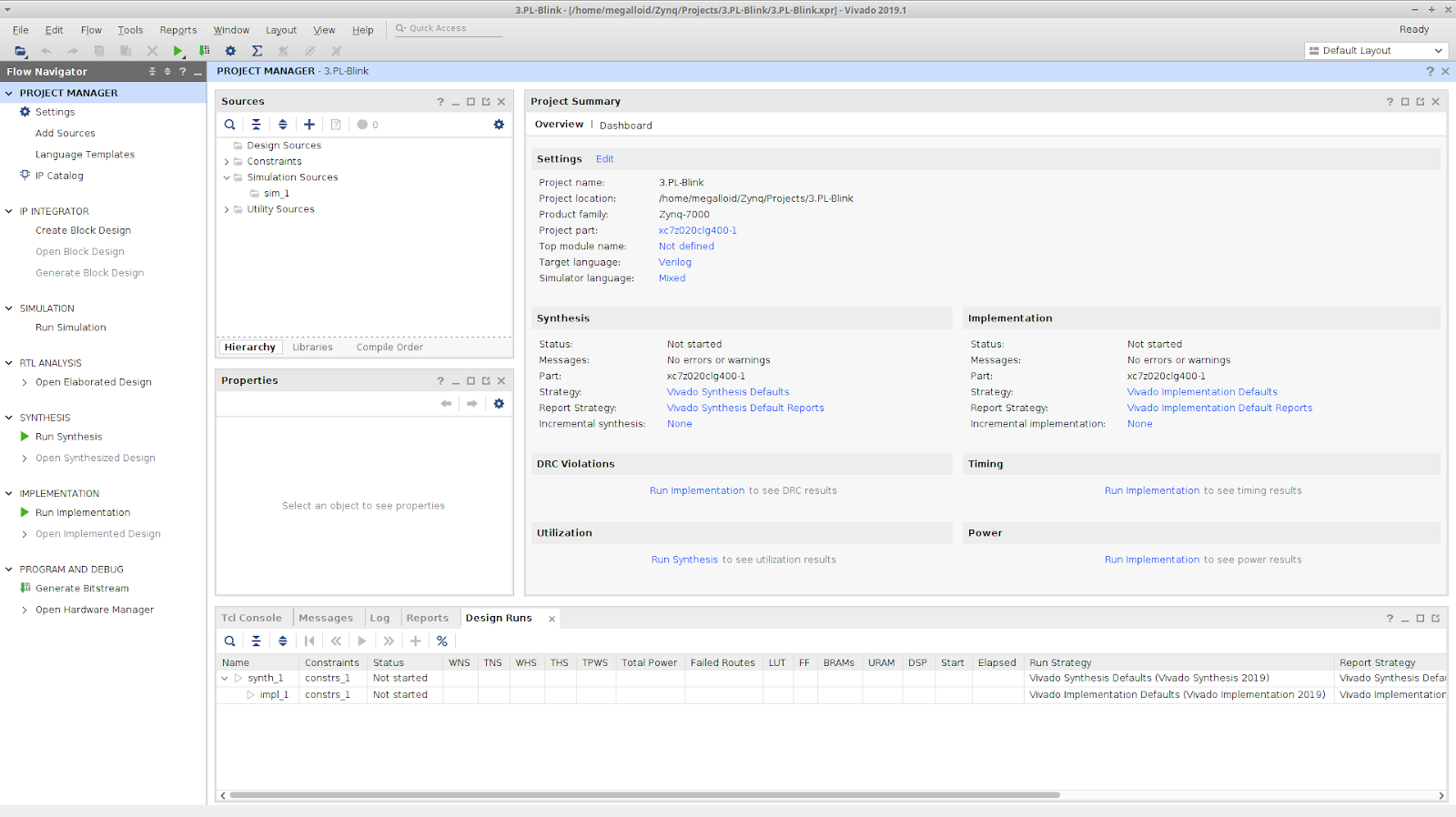

Vivado . File - Project - New…

, Next > PL-Blink.

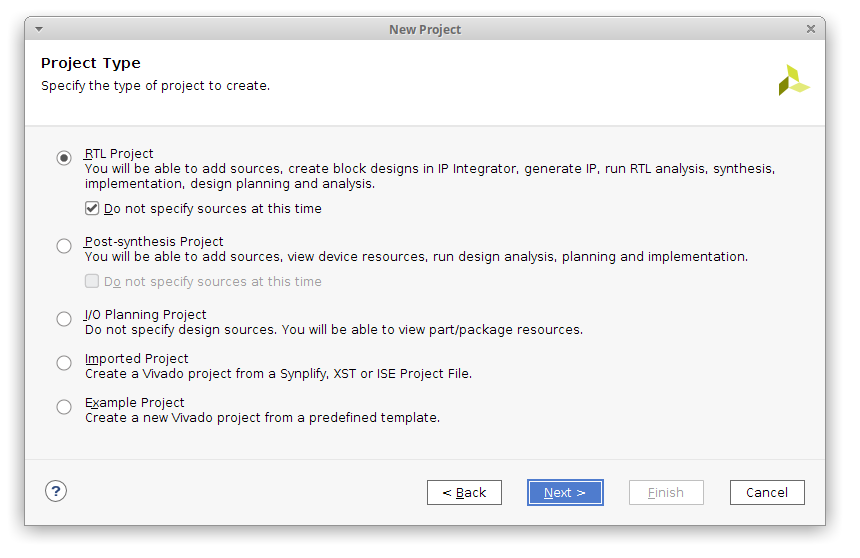

RTL Project Do not specify sources at this time.

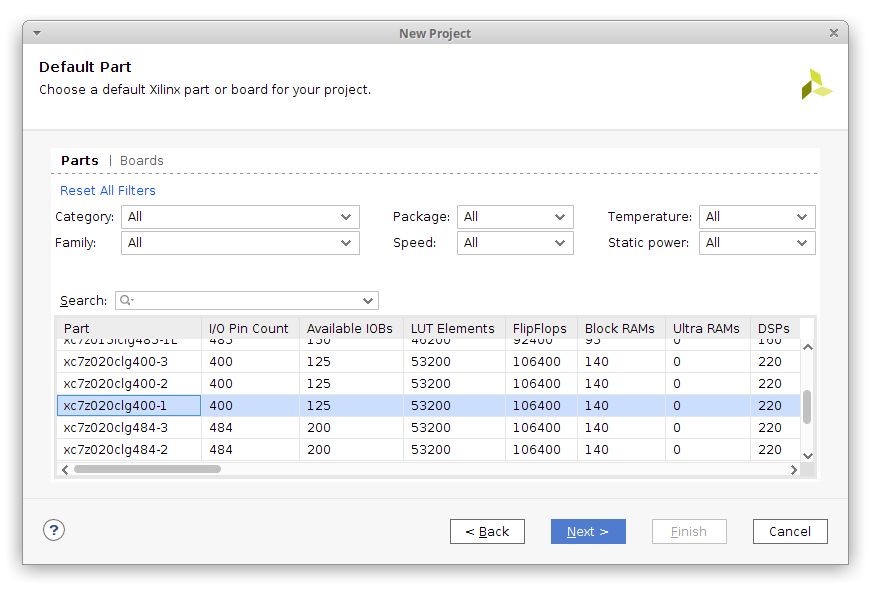

xc7z020clg400-1.

Finish.

Vivado !

, , , =)

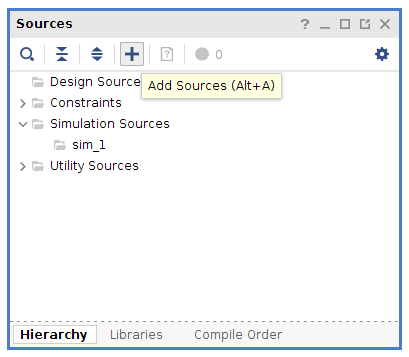

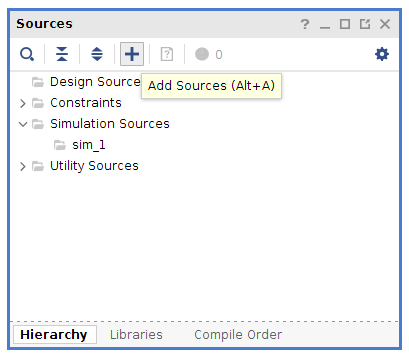

Sources Add Sources.

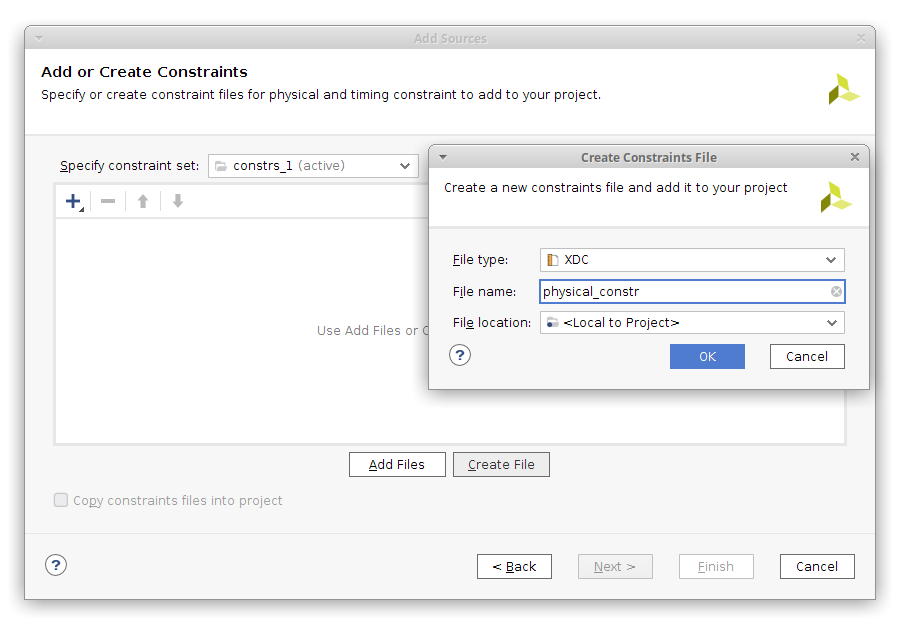

Add or create constraints.

Create file physical_constr. .

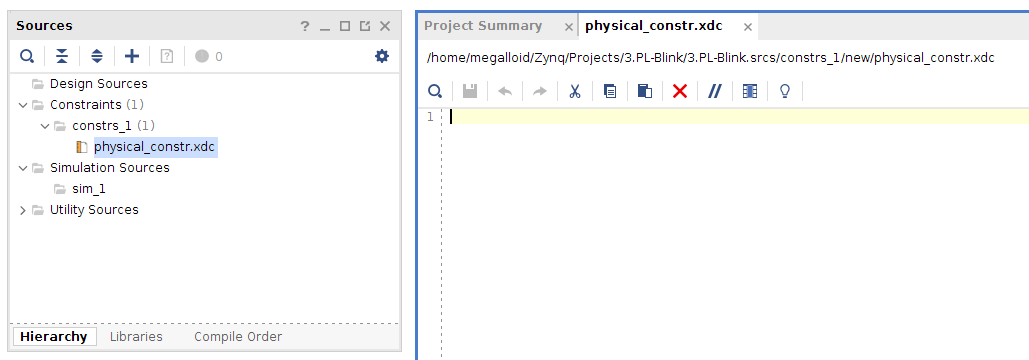

Finish Soures :

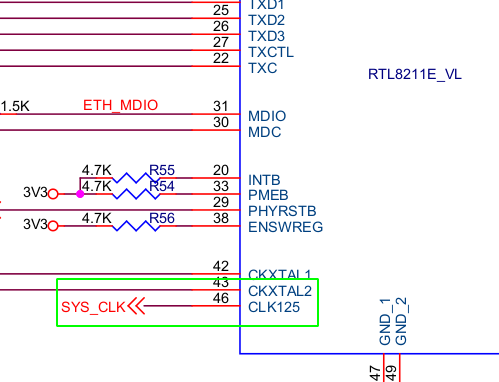

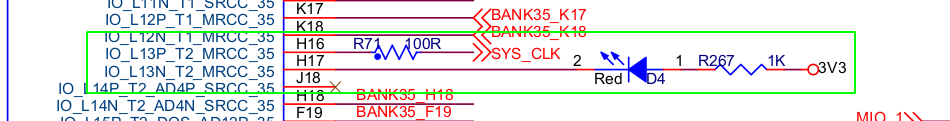

, , . , , Ethernet- RTL8211E-VL PLL, 125 H16 (IO_L13P_T2_MRCC_35). ? =)

, .

, , H17 (IO_L13N_T2_MRCC_35) , .

. constraints- :

# User LED and Clock

set_property IOSTANDARD LVCMOS33 [get_ports led_h17_d4]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN H17 [get_ports led_h17_d4]

set_property PACKAGE_PIN H16 [get_ports sys_clk]

, , , , .

, get_ports ( ). , Verilog-.

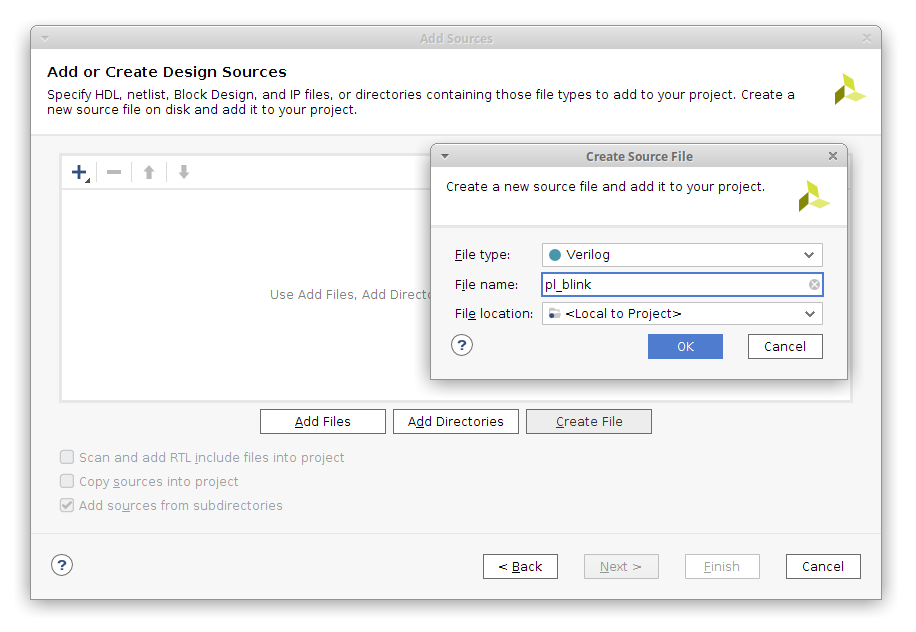

Design Source. Sources Add Sources.

Add or create design sources. Create File, , Verilog. Finish.

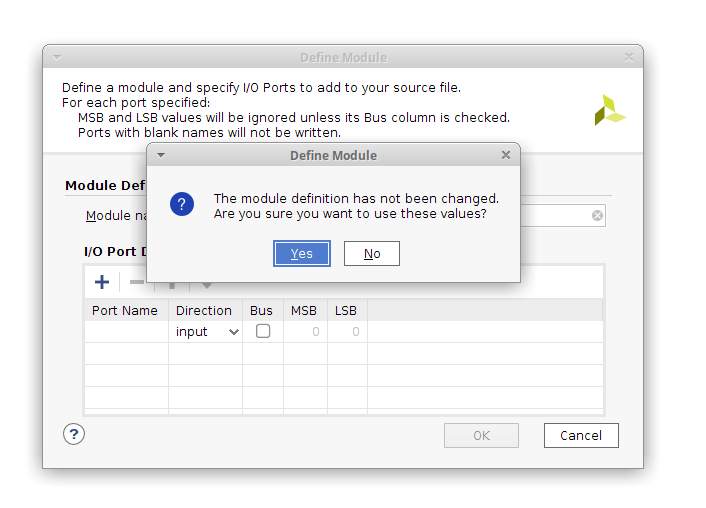

Yes.

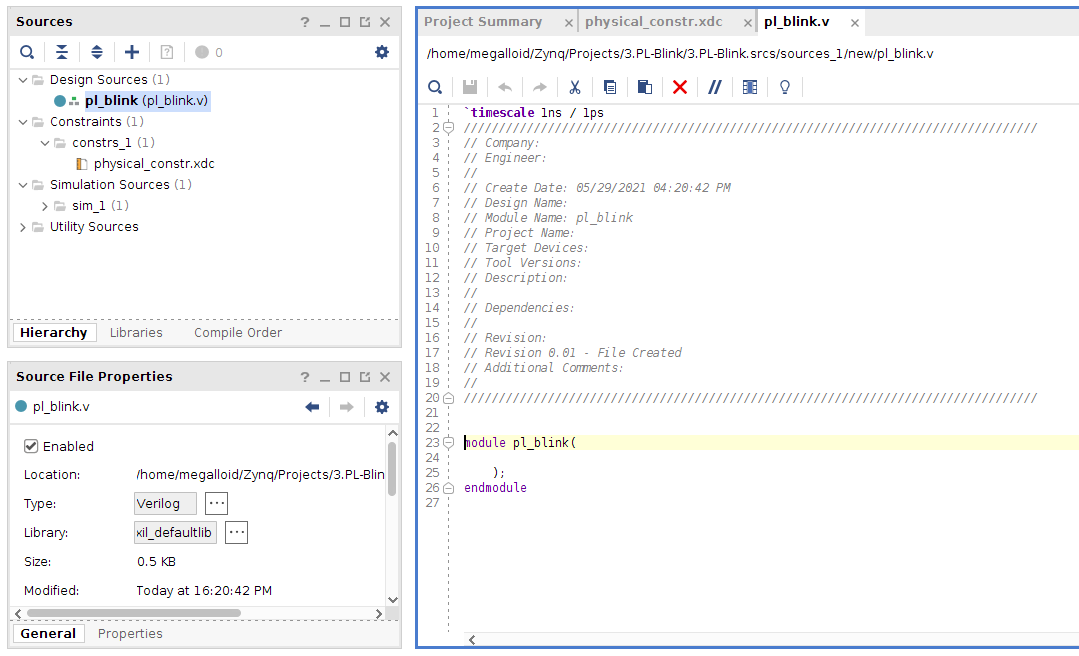

:

Verilog- :

// , Verilog.

// , .

`timescale 1ns / 1ps

// - ( ++)

module pl_blink(input sys_clk, output led_h17_d4);

//

reg r_led;

// ,

reg [31:0] counter;

//

initial begin

counter <= 32'b0; //

r_led <= 1'b0; //

end

// ,

always@(posedge sys_clk)

begin

counter <= counter + 1'b1; //

if(counter > 12000000) //

begin

r_led <= !r_led; //

counter <= 32'b0; //

end

end

assign led_h17_d4 = r_led; // ()

endmodule

Ctrl + S . , . - , Zynq .

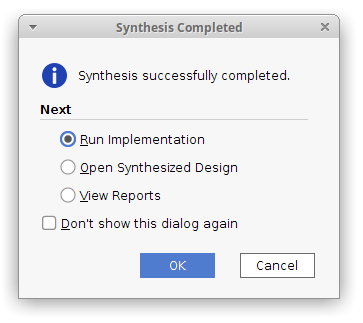

Run Synthesis . , :

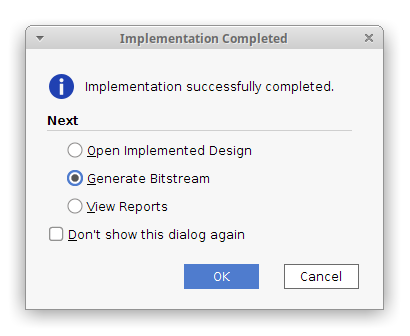

Run implementation . Generate Bitstream :

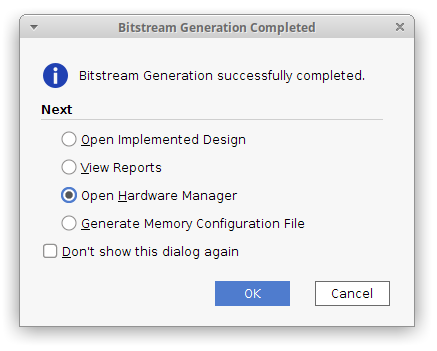

, , Open Hardware Manager :

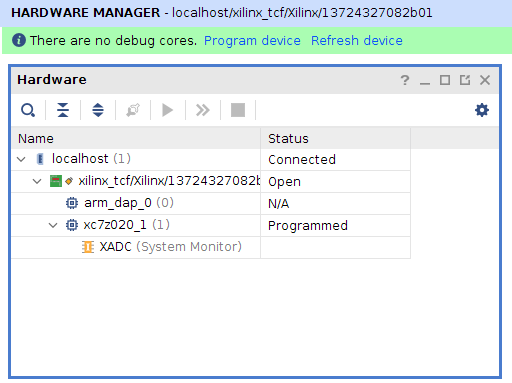

Hardware Manager Auto connect, :

Klicken Sie im Menü links oder durch Klicken mit der rechten Maustaste auf xc7z020_1 im Menü Hardware auf das Element Gerät programmieren .

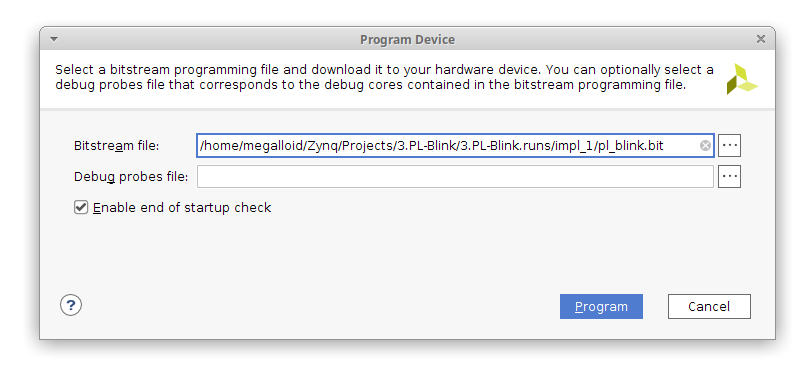

Stellen Sie im nächsten Fenster sicher, dass der Pfad zur Bitstream-Datei korrekt angegeben ist, und klicken Sie auf die Schaltfläche Programm.

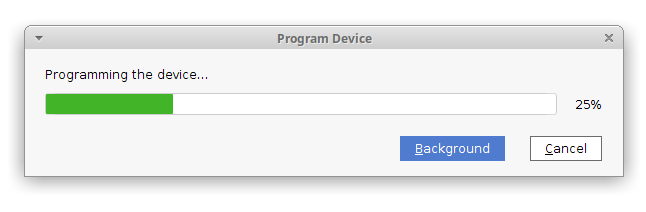

Das Programm wird auf unser Board hochgeladen ...

Und nach einem Moment leuchtet die D2-LED auf der Platine auf, was uns darüber informiert, dass „FPGA DONE“ und am anderen Ende der Platine eine fröhlich blinkende LED zu sehen ist. =)

Im Allgemeinen kann die Aufgabe als erledigt betrachtet werden. Ich denke, wenn ich die Verilog-Sprache beherrsche und alle neuen Probleme mit diesem Board löse, kann ich Ihnen wieder gefallen.