IBM kündigte die Entwicklung einer 2-nm-Prozesstechnologie an.

Was angekündigt wurde:

- 2 nm.

- 50 Milliarden Transistoren in einem nagelgroßen Bereich. Später stellten sie auf einer Fläche von 150 Quadratmetern klar, dass 333 Millionen Transistoren pro Quadratmillimeter (

- MTx / mm 2 ).

- Der Gate-Abstand des Transistors (Contacted Poly Pitch, CPP) beträgt 44 nm, die Gate-Länge beträgt 12 nm.

- (Gate All Around, GAA). – , IBM (horizontal nanosheets, HNS).

- HNS .

- 45% 75% 7 .

- (EUV) HNS 15 70 . , SRAM.

- 5 .

Ist das wirklich eine 2nm Prozesstechnologie? Heute ist TSMC führend in der Chipherstellung. Wir haben die Beziehung zwischen TSMC-Prozessnamen und Transistordichte durch Approximation der Kurve mit einem Bestimmungskoeffizienten von 0,99 aufgetragen.

Von 28 nm bis 5 nm werden die tatsächlichen Zahlen gemäß IC Knowledge und TechInsights verwendet. 3-nm-Zahlen basieren auf Pressemitteilungen von TSMC. 2 nm und 1,5 nm ist unsere Extrapolation.

Mithilfe des Diagramms können Sie die Dichte von Transistoren in eine äquivalente TSMC-Prozesstechnologie (TSMC Equivalent Node oder TEN) umwandeln. Wir erhalten 2,9 nm für 333 MTx / mm 2 . Aus unserer Sicht stellt sich heraus, dass es sich um eine 3-nm-Prozesstechnologie handelt, nicht um 2-nm-Verfahren.

Um die Ankündigung von IBM mit früheren Ankündigungen der 3-nm-Prozesstechnologie und des vorgeschlagenen 2-nm-Prozesses genauer zu vergleichen, müssen mehrere Annahmen getroffen werden.

- Aus der Ankündigung ist bekannt, dass der CPP 44 nm beträgt.

- Angenommen, die Produktion verwendet die engste Transistorplatzierungstechnologie, Single Diffusion Break (SDB).

- Basierend auf dem ausgeschnittenen Foto aus der Ankündigung wird die Buried Power Rails (BPR) -Technologie nicht verwendet. Der BPR wird benötigt, um die HNS-Spurgröße auf 5,0 zu reduzieren. Nehmen wir also an, dass dieser Wert in diesem Prozess 6,0 beträgt.

- Um eine Dichte von 333 MTx / mm 2 zu erreichen , müsste der minimale Metallabstand 18 nm betragen - ein sehr aggressiver Wert, der wahrscheinlich eine EUV-Mehrmatrix-Photolithographie erfordern würde.

2-nm-IBM im Vergleich zur vorhandenen 3-nm-Prozesstechnologie

In der folgenden Tabelle werden IBM-Designs mit unseren 3-nm-Prozessschätzungen von Samsung und TSMC verglichen. Wir wissen, dass Samsung auch mit HNS zusammenarbeitet, und TSMC hat sich für einen 3-nm-FinFET entschieden. Samsung und TSMC kündigten außerdem eine Erhöhung der Transistordichte um 3 nm für ihre Prozesstechnologie im Vergleich zu 5 nm an. Daher ist uns die Dichte der Transistoren aller drei Unternehmen bekannt, und wir können die TEN für alle berechnen. IBMs TEN beträgt 2,9; Es ist zu sehen, dass Samsung 4.7 und TSMC 3.0 hat. Wieder stellt sich heraus, dass 2 nm von IBM 3 nm von TSMC ähnlicher sind, während Samsung hinterherhinkt.

Indikative Parameter, die zur Erreichung der angekündigten Dichten erforderlich sind, werden rot hervorgehoben, sofern alle Unternehmen die SDB-Technologie verwenden. Die Höhe der Spuren ist in TSMC am kleinsten, da dieser Parameter ohne BPR im FinFET 5,0 erreichen kann. Damit der HNS dieselbe Höhe hat, muss BPR verwendet werden.

2-nm-IBM im Vergleich zur vorhandenen 2-nm-Prozesstechnologie

In der folgenden Tabelle haben wir die Parameterwerte für die 2-nm-Prozesstechnologie von Samsung und TSMC geschätzt. Bei unserer Extrapolation gehen wir davon aus, dass Unternehmen BPR verwenden (die BPR-Technologie ist noch nicht ausgereift, wird aber wahrscheinlich online gehen, wenn sie 2023-2024 einen 2-nm-Prozess ankündigt). Nehmen wir außerdem an, dass Unternehmen die NHS-Forksheet-Architektur (HNS FS) verwenden, um eine Spurhöhe von 4,33 zu erreichen. CPP- und MPP-Schätzungen basieren auf aktuellen Trends bei der Miniaturisierung von Technologien.

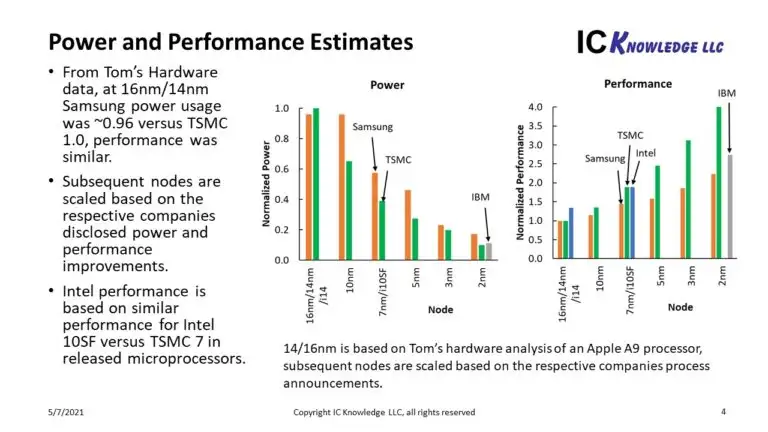

Stromverbrauch und Leistung

In diesem Jahr habe ich bereits anhand zusätzlicher Leistungsdaten von Intel Vermutungen zum Stromverbrauch und zur Leistung von Geräten von Samsung und TSMC angestellt. Die Extrapolation basiert auf Zusicherungen von Unternehmen und auf realen Vergleichen zwischen 14-nm- und 16-nm-Prozessen.

Da IBM die Verbesserungen des Stromverbrauchs und der Leistung mit fortschrittlichen 7-nm-Herstellungsprozessen verglichen hat, kann ich deren Daten in denselben Diagrammen darstellen.

Durch die Verwendung von HNS konnte IBM erhebliche Energieeinsparungen erzielen, wodurch der 2-nm-Prozess effizienter als der 3-nm-Prozess von Samsung und TSMC wurde. Wenn TSMC unserer Meinung nach bei 2 nm auf HNS umschaltet, ist ihr Stromverbrauch dem von IBM nicht unterlegen. In Bezug auf die Leistung gehen wir davon aus, dass der 3-nm-Prozess von TSMC den 2-nm-Prozess von IBM übertreffen wird.

Natürlich sind dies alles nur Schätzungen, die auf einer Vielzahl von Annahmen beruhen.

Fazit

Nach der Analyse der IBM-Ankündigung kommen wir zu dem Schluss, dass ihre 2-nm-Prozesstechnologie hinsichtlich der Dichte der Transistoren der 3-nm-Prozesstechnologie von TSMC ähnlicher ist, während sie die besten Stromverbrauchsindikatoren aufweist, jedoch eine geringere Geschwindigkeit aufweist. Die Aussage von IBM ist beeindruckend - dies ist jedoch nur eine Laborprobe, die 3 nm von TSMC nur beim Stromverbrauch deutlich übertrifft. Gleichzeitig erscheinen in diesem Jahr die ersten riskanten Chargen von 3-nm-Geräten von TSMC und im nächsten Jahr kommerzielle.

Unserer Meinung nach wird TSMC den Vorteil in Bezug auf Dichte, Stromverbrauch und Geschwindigkeit von Geräten beibehalten, die auf der 2-nm-Prozesstechnologie basieren, wenn sie 2023-2024 in Produktion gehen.