Paradigma

Es ist sehr wichtig zu betonen, dass der Maschinencode in einer relativ fließenden subjektiven Wahrnehmung als Pseudocode in den Feldern der Dump-Tabellen aussehen und so wenig wie möglich die Esoterizität von Bitfeldern angeben sollte.

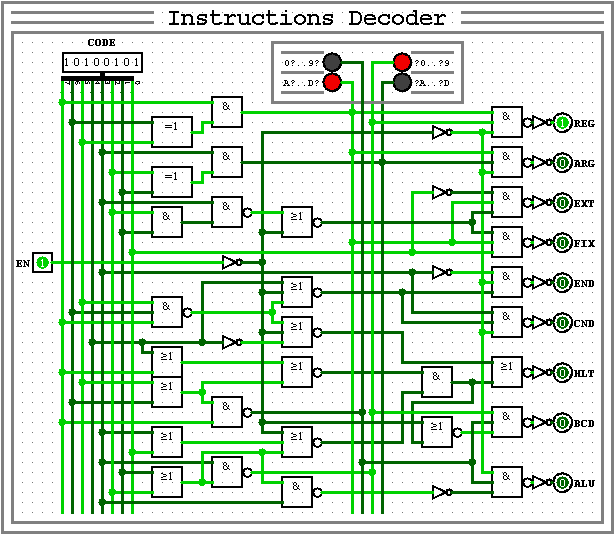

Befehlsdecoder

Eines der wichtigsten und wichtigsten Elemente eines Automaten ist ein Gerät zum Dekodieren genau dieser Aktion zu einem bestimmten Zeitpunkt, den der Programmierer selbst im Sinn hatte, als er die Reihenfolge dieser Befehle in seinen Algorithmen zusammenstellte.

Zunächst muss eine Skizze des Koda-Koyaaniskatsi- Decoders in Logisim unter Verwendung der am besten zugänglichen Logikelemente aus der Nomenklatur der TTL-Serie erstellt werden, um eine einfache Montage des Decoders auf realen Mikroschaltungen zu gewährleisten.

Hier erstellen wir eine bedingte grafische Bezeichnung für den Decoder, die erforderlich ist, um in Zukunft die Kompaktheit und Klarheit des gesamten Schaltkreises der Maschine zu gewährleisten und den korrekten Betrieb der Decodierung aller 256 Befehlscodes zu überprüfen.

Zeitlose Präfixregister

Wenn der visuelle Test der Leistung des Decoders gut und ohne sichtbare Fehler verlief, war es an der Zeit, die Hauptregister zum Speichern der Indizes der aktiven ROZ anzuschließen, die durch die Befehle der REG-Gruppe als Architekturpräfixe ausgelöst werden.

Um die Speicherung von Vektoren des Datenroutings durch ALU- und RAM-Befehle sicherzustellen, werden ein weiteres Register und zwei verknüpfte Multiplexer hinzugefügt, mit denen Sie beliebige Register beliebiger Gruppen als Befehlsoperanden verknüpfen können.

Diese Register sind für sich genommen nicht dazu gedacht, die Ergebnisse von Berechnungen zu speichern und eine Art Rolle als Zeiger auf die erforderlichen Register zu spielen, um eine kontrollierte Interaktion im Programm zwischen allen verfügbaren ROZ und / oder Speicher bereitzustellen.

Architektonischer Zustand

Um die normale Programminteraktion aller Register sicherzustellen, muss eine Registerdatei mit zwei Ports vorhanden sein, die nicht in den Logisim-Bibliotheken enthalten ist, sodass wir nach anderen mehr oder weniger kostspieligen alternativen Lösungen suchen müssen. Der klassische Koyaaniskatsi verfügt über eine recht komplexe Registerdatei, die hier nicht als anschauliches Beispiel betrachtet wird und die Entwicklung einer neuen Lösung zum Organisieren einer mehrzyklischen Registerdatei mit langsamem Zugriff erfordert. Da sich das Schema als ein Zyklus herausstellte, ist es ziemlich schwierig, die Registerdatei im RAM hier zu organisieren, und es wird notwendig, ein Mehrzyklusschema zu erstellen, bei dem sich viele spezielle Zyklen in einer genau festgelegten Reihenfolge gegenseitig ersetzen.

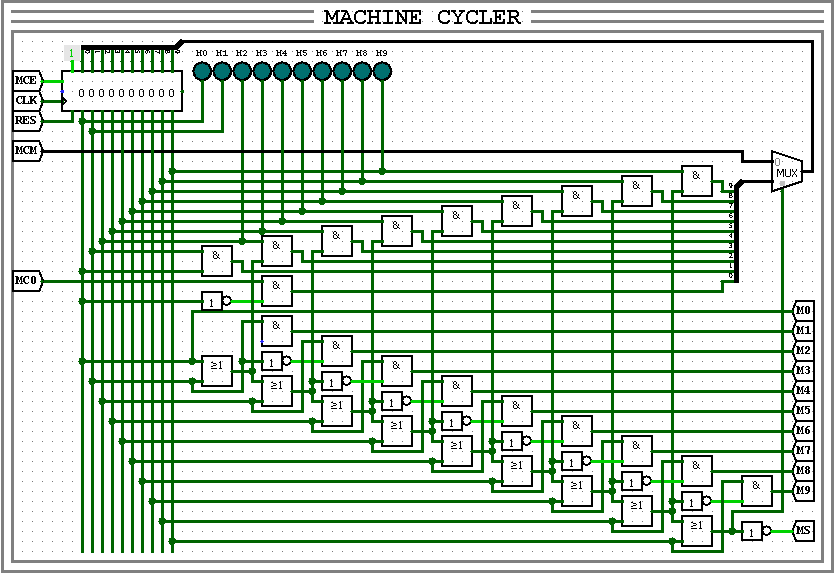

Der algorithmische Ausdruck des Zykluszählers kann als "m & = m - 1" mit sequentiellem Abschalten aller aktiven Bits des Architekturzustands beschrieben werden, wobei zu einem bestimmten Zeitpunkt des Maschinenzyklus nur Schlüsselknoten der Schaltung aktiviert werden.

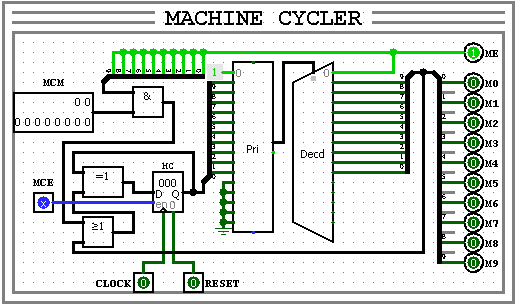

Der maximal erweiterte Prototyp des Maschinenzykluszählers kann auf einer Skizze einer ähnlichen Schaltung dargestellt werden, deren Logik der Funktionsweise nur schwer zu verstehen ist.

Eine ähnliche Skizze kann als optimalste und universellste Option dienen:

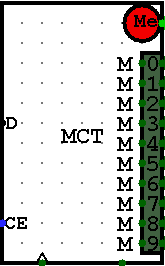

Für die Verwendung im Schema kann die bedingte grafische Bezeichnung wie folgt lauten:

Mit Hilfe von 3-ODER-Logikgattern ist es nun möglich, das Signal jedes Befehls in die Bitmaske der für die korrekte Ausführung des Befehls erforderlichen Zyklen zu übersetzen, für deren gesamte Ausführungsdauer der Befehlszähler vorübergehend ausgesetzt wird.

Fazit

Wie Sie sehen, müssen wir, um zumindest mehr oder weniger die Nuancen der Selbstkonstruktion eines programmierbaren Automaten zu verstehen, nur mit Grundkenntnissen auf den Ebenen des Zeichnens des Schemas einer blinkenden Weihnachtsbaumgirlande auskommen. Hier wurden bewusst keine allen bekannten Referenzmaterialien verwendet, so dass der kreative Prozess aufregender und frei von allen Welttrends und -trends war und nicht alle möglichen Fehleinschätzungen oder Fehler berücksichtigt wurden.

Im nächsten Teil werde ich versuchen, meine schrittweise Konstruktion des "Akyn-Prozessors" fortzusetzen,

da der neue Entwurf fast für mich funktioniert, aber ich habe beschlossen, ihn von Grund auf neu zu zeichnen

und gleichzeitig alle wichtigen Phasen zu dokumentieren ...