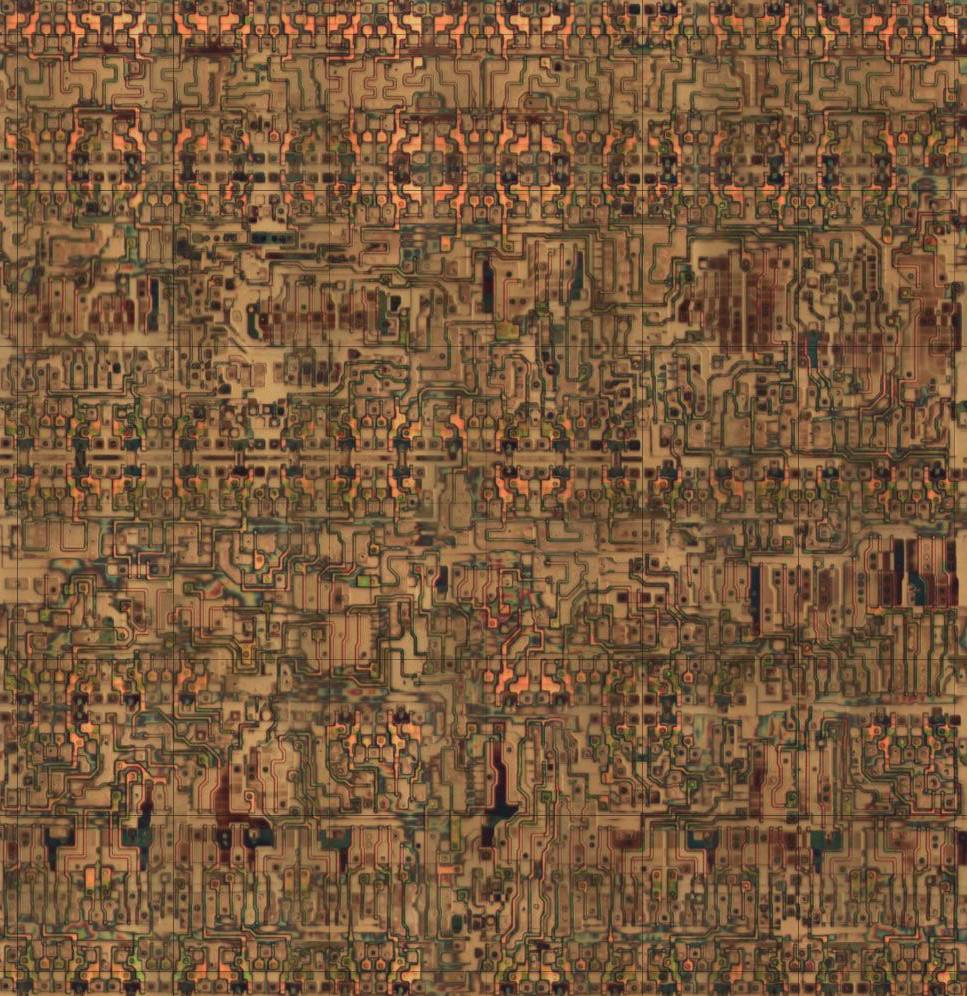

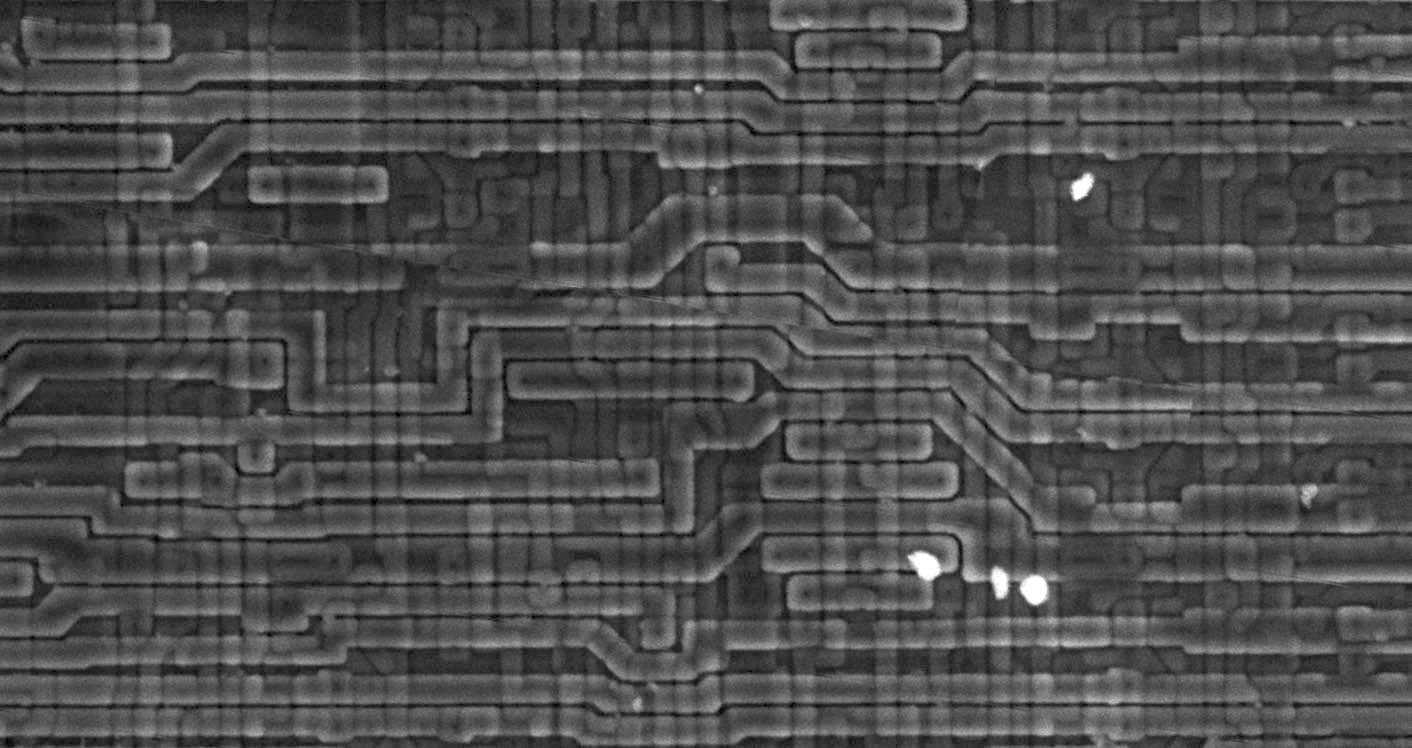

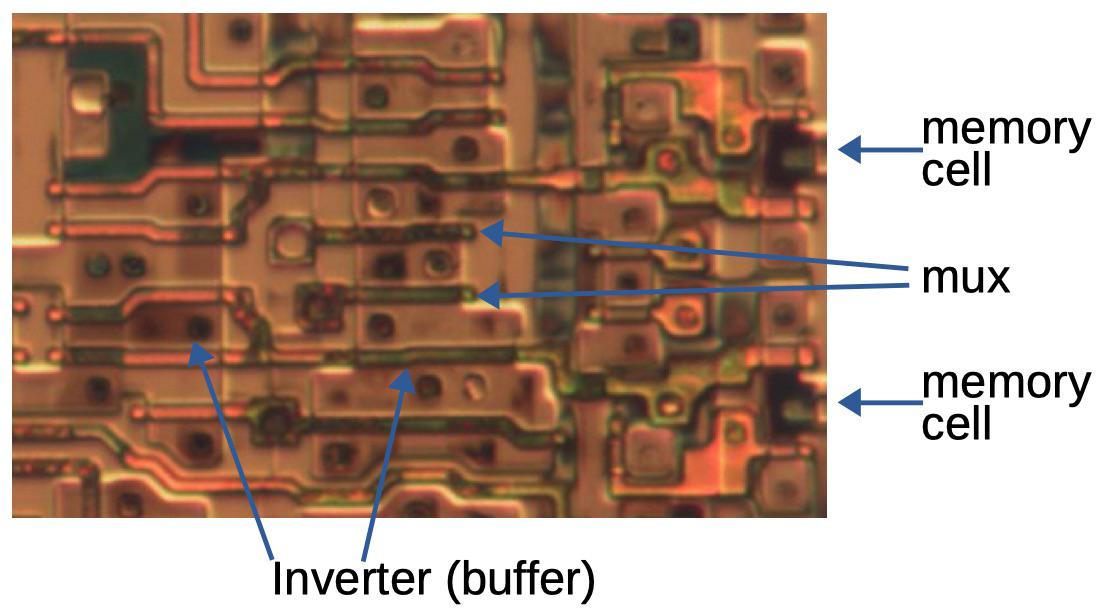

Das Foto zeigt einen der 64 Blöcke des XC2064-Chips. Die Metallisierungsschichten werden entfernt, wir können Silizium- und Polysiliziumtransistoren sehen, die unter der Metallisierung liegen. Sie können hier ein größeres Foto sehen: siliconpr0n .

Das FPGA wurde 1984 von Ross Freeman, Mitbegründer von Xilinx, erfunden. Das erste FPGA war das XC2064. Es war viel einfacher als moderne FPGAs, enthielt nur 64 Logikblöcke im Vergleich zu den Tausenden und Millionen moderner FPGAs, und seine Schaffung führte zur Entstehung einer Branche im Wert von Milliarden von Dollar. Der XC2064 ist so wichtig, dass er in die Chips Hall of Fame aufgenommen wurde. Ich habe den XC2064 rückentwickelt und in diesem Beitrag erkläre ich seine interne Struktur allgemein und wie er mit einem Bitstream programmiert wird.

Xilinx

Xilinx -. , , Xilinx , . Xilinx Seiko Epson Semiconductor Division ( Seiko Epson).

XC2064

: ( ) . — (Programmable Logic Devices, PLD), , , 1967 . , , , . , PROM, , , EPROM, . , , Programmable Logic Array, Programmable Array Logic (1978), Generic Array Logic Uncommitted Logic Array. , , « », . , , , , , . , . "Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology." "A Brief History of FPGAs".

Xilinx XC2064 ist der erste FPGA-Chip. Von hier genommen: siliconpr0n .

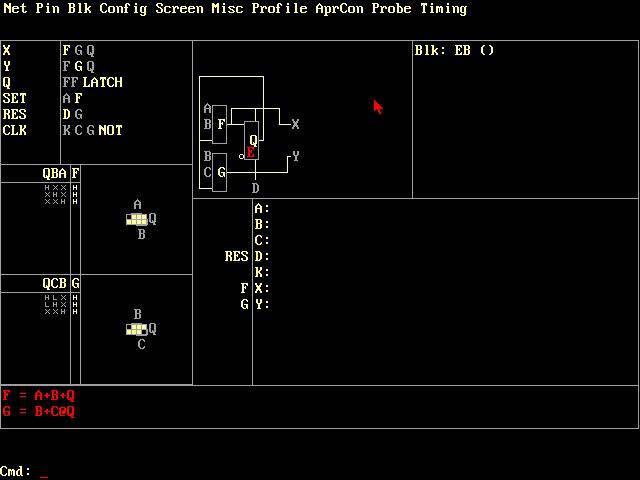

FPGAs sind jetzt in Hardwarebeschreibungssprachen wie Verilog oder VHDL programmiert. Zu dieser Zeit stellte Xilinx jedoch eine eigene Entwicklungssoftware zur Verfügung, eine MS-DOS-Anwendung namens XACT, für die stolzen 12.000 US-Dollar. XACT arbeitete auf einer niedrigeren Ebene als moderne Tools: Der Benutzer definierte die Funktion jedes logischen Blocks, wie im folgenden Screenshot gezeigt, und die Verbindungen zwischen den logischen Blöcken.

XACT leitete die Verbindungen weiter und generierte eine Konfigurationsdatei (Bitstream), die in das FPGA geladen wurde.

Screenshot von XACT. Die beiden Tabellen F und G implementieren die am unteren Bildschirmrand gezeigten Gleichungen, wobei die Karnaugh-Karte oben gezeigt ist.

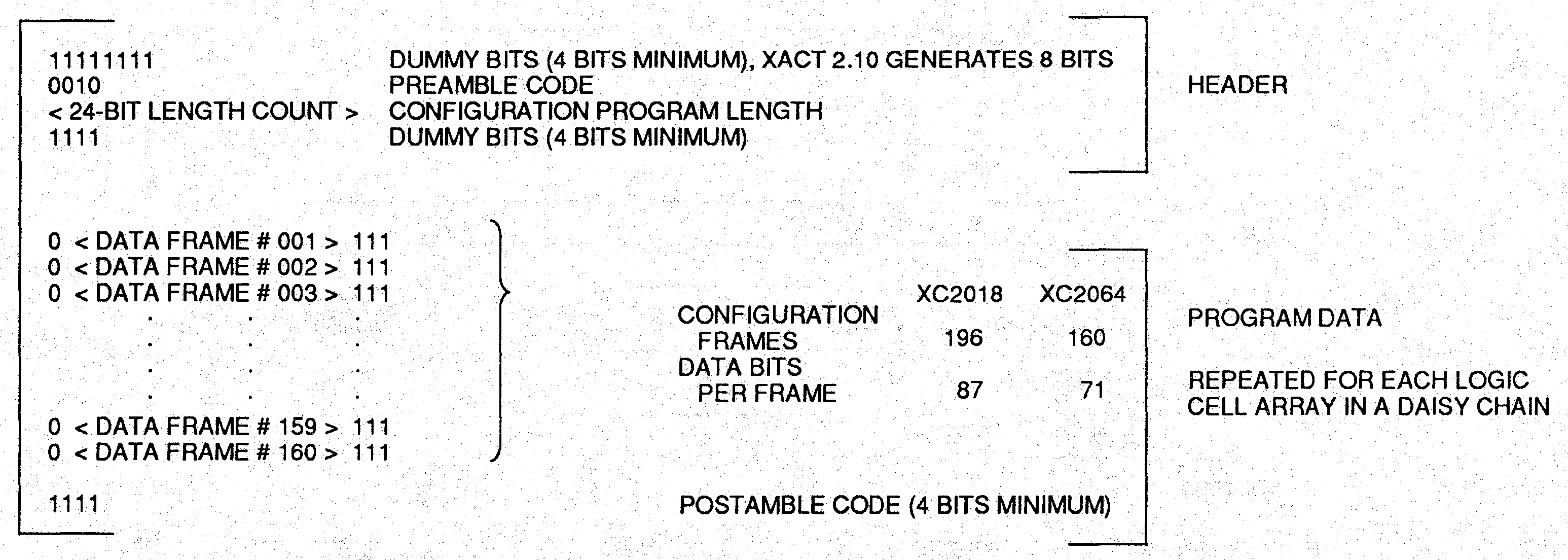

Das FPGA wurde unter Verwendung eines Bitstroms konfiguriert, einer Folge von Bits in einem proprietären Format. Wenn Sie sich den XC2064-Bitstrom (unten) ansehen, sehen Sie eine mysteriöse Mischung von Mustern, die sich unregelmäßig wiederholen und über den Bitstrom verteilt sind. Das Studium der physikalischen Schaltkreise von FPGAs zeigt jedoch die Datenstruktur des Bitstroms und kann untersucht werden.

Ein Teil des von XACT erzeugten Bitstroms.

Wie funktioniert FPGA?

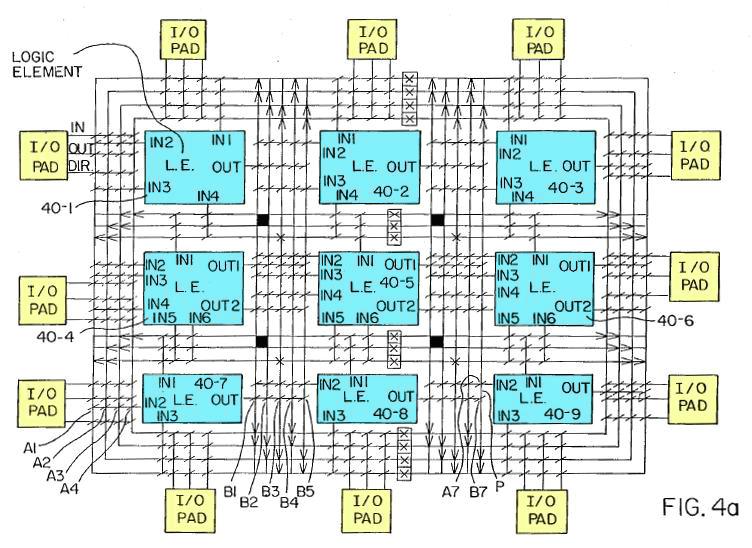

Die folgende Abbildung aus dem ursprünglichen FPGA-Patent zeigt die Grundstruktur eines FPGA. Dieses vereinfachte FPGA verfügt über insgesamt 9 Logikblöcke (blau markiert) und 12 E / A-Ports. Ein Verbindungsnetzwerk verbindet Komponenten miteinander. Durch Setzen von Schaltern (diagonale Linien) an den Verbindungen können Logikblöcke miteinander und mit den E / A-Ports verbunden werden. Jedes Logikelement kann für die gewünschte Logikfunktion programmiert werden. Infolgedessen kann ein solcher programmierbarer Chip jedes Gerät implementieren, das in den verfügbaren Raum passt.

FPGA-Patent , logische Blöcke (LE) miteinander verbunden.

Konfigurierbarer Logikblock (CLB)

Obwohl das obige Bild 9 CLBs zeigt, verfügt der XC2064 über 64 CLBs. Die folgende Abbildung zeigt die Struktur der CLB. CLB hat 4 Eingänge (A, B, C, D) und zwei Ausgänge (X und Y). Dazwischen liegt eine kombinatorische Logik, die auf jede gewünschte Logikfunktion programmiert werden kann. Die CLB enthält auch einen Trigger, mit dessen Hilfe Sie Zähler, Schieberegister, Zustandsautomaten und andere Zustandsschaltungen implementieren können. Trapeze kennzeichnen Multiplexer, die so programmiert werden können, dass sie ein Signal von einem der Eingänge weiterleiten. Mit Multiplexern können Sie die CLB für eine bestimmte Aufgabe konfigurieren, indem Sie bestimmte Signale zur Steuerung des Triggers und der Ausgänge auswählen.

Konfigurierbarer Logikblock in XC2064, hier entnommen: Datenblatt .

Sie fragen sich vielleicht, wie kombinatorische Logik beliebige Logikfunktionen implementiert. Gibt es eine Wahl zwischen einer Reihe von AND, OR, XOR und so weiter? Nein, es gibt einen netten Trick, der als Nachschlagetabelle (LUT) bezeichnet wird und eigentlich eine Wahrheitstabelle für eine Funktion ist. Beispielsweise wird eine Funktion von drei Variablen durch eine Tabelle mit 8 Zeilen definiert. Die LUT enthält 8 Speicherbits. Wir können jede Logikfunktion mit 3 Eingängen implementieren, während diese drei Bits beibehalten werden.

Tabellen anzeigen

XC2064 — , . CLB . XC2064 , 4 . , .

XC2064 . .

XC2064 . .

Verbindungen

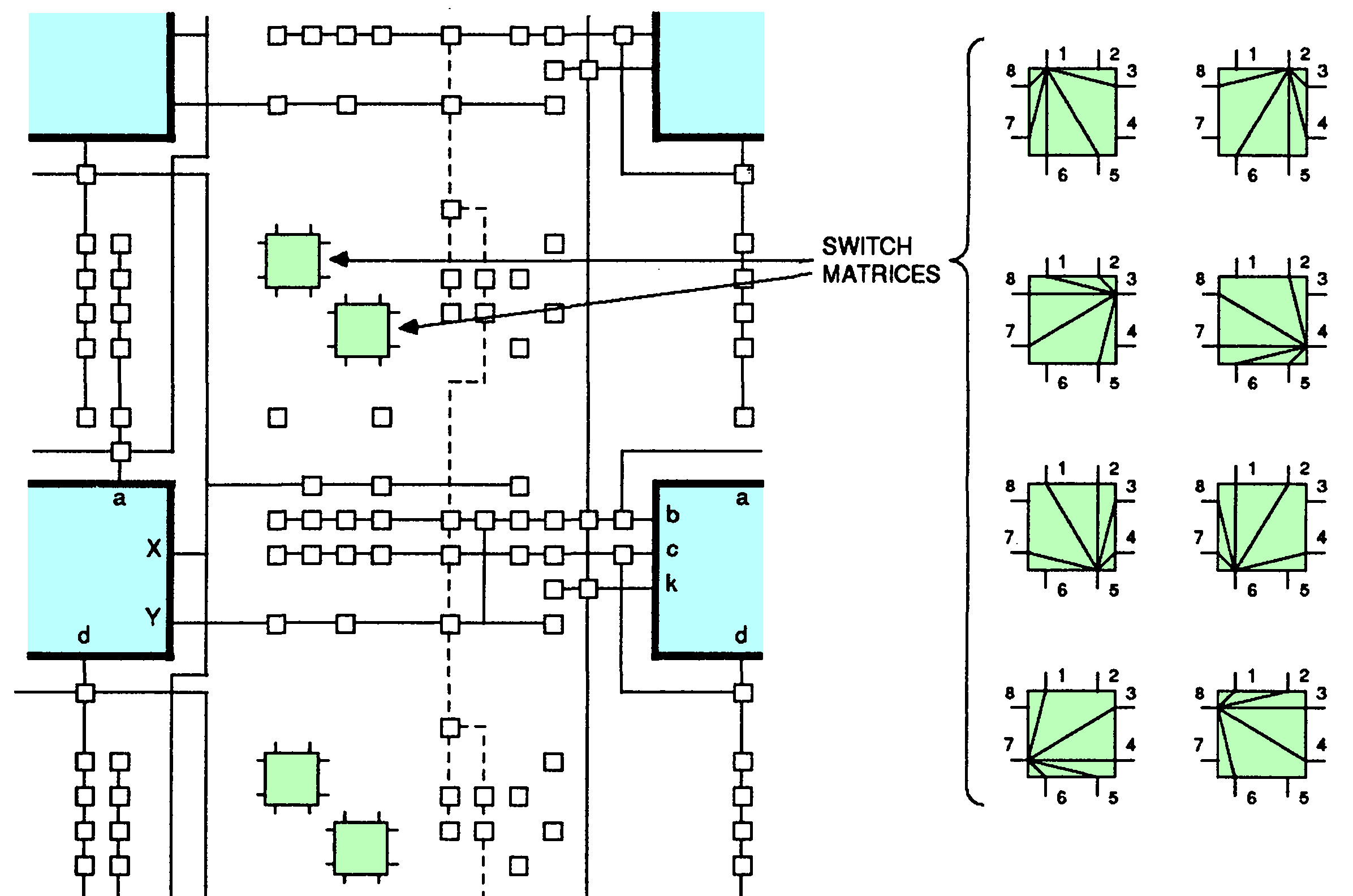

Der nächste wichtige Aspekt von FPGAs sind die Verbindungen, die so programmiert werden können, dass sie die CLB auf verschiedene Arten schalten. Die Verbindungen sind komplex, aber die grobe Beschreibung ist, dass es Segmente vertikaler und horizontaler Verbindungen zwischen allen CLBs gibt. Sie können CLB mit horizontalen und vertikalen Linien verbinden und beliebige Verbindungen erstellen. Eine komplexere Art der Verbindung ist die "Switch-Matrix". Jede Matrix hat 8 Pins, die (fast) auf irgendeine Weise miteinander verbunden werden können.

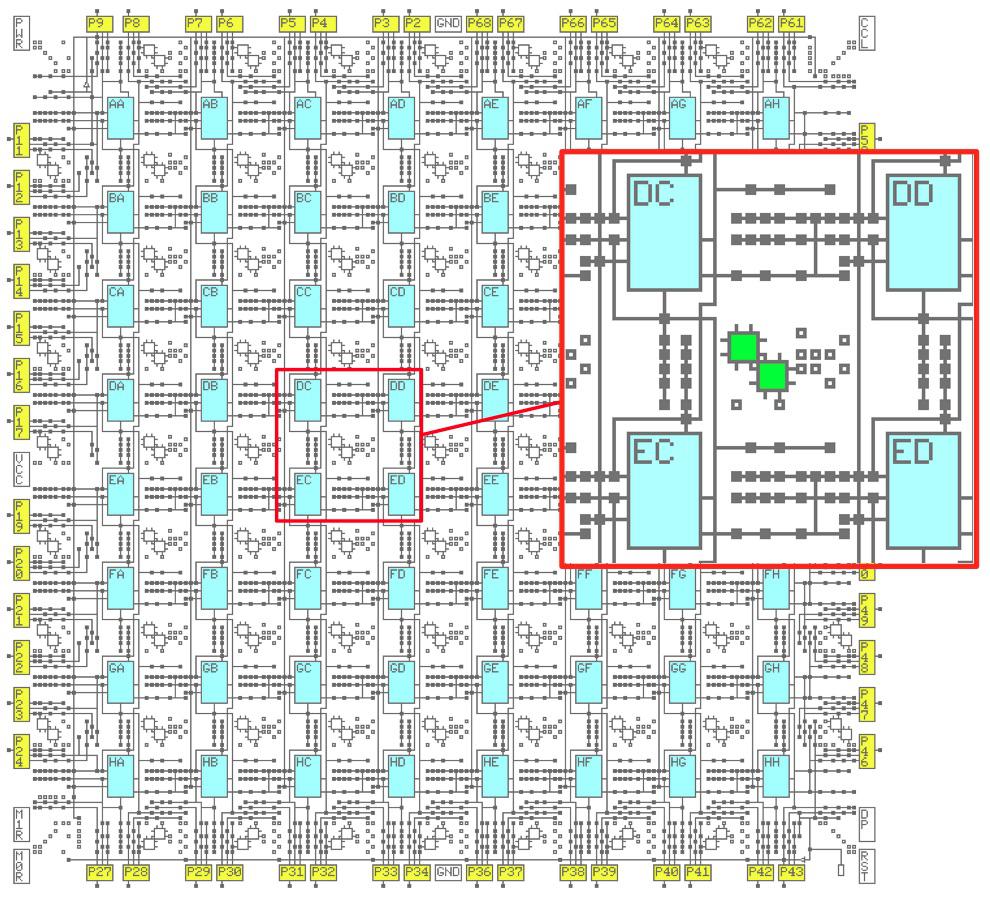

Die folgende Abbildung zeigt die Struktur der XC2064-Verbindungen, die Verbindungen zwischen Logikblöcken (blau) und E / A-Leitungen (gelb) herstellen. Der Einschub zeigt die Details des Kopplungsmechanismus. Die grünen Rechtecke sind 8-polige Schaltmatrizen und die kleinen Quadrate sind programmierbare Verbindungspunkte.

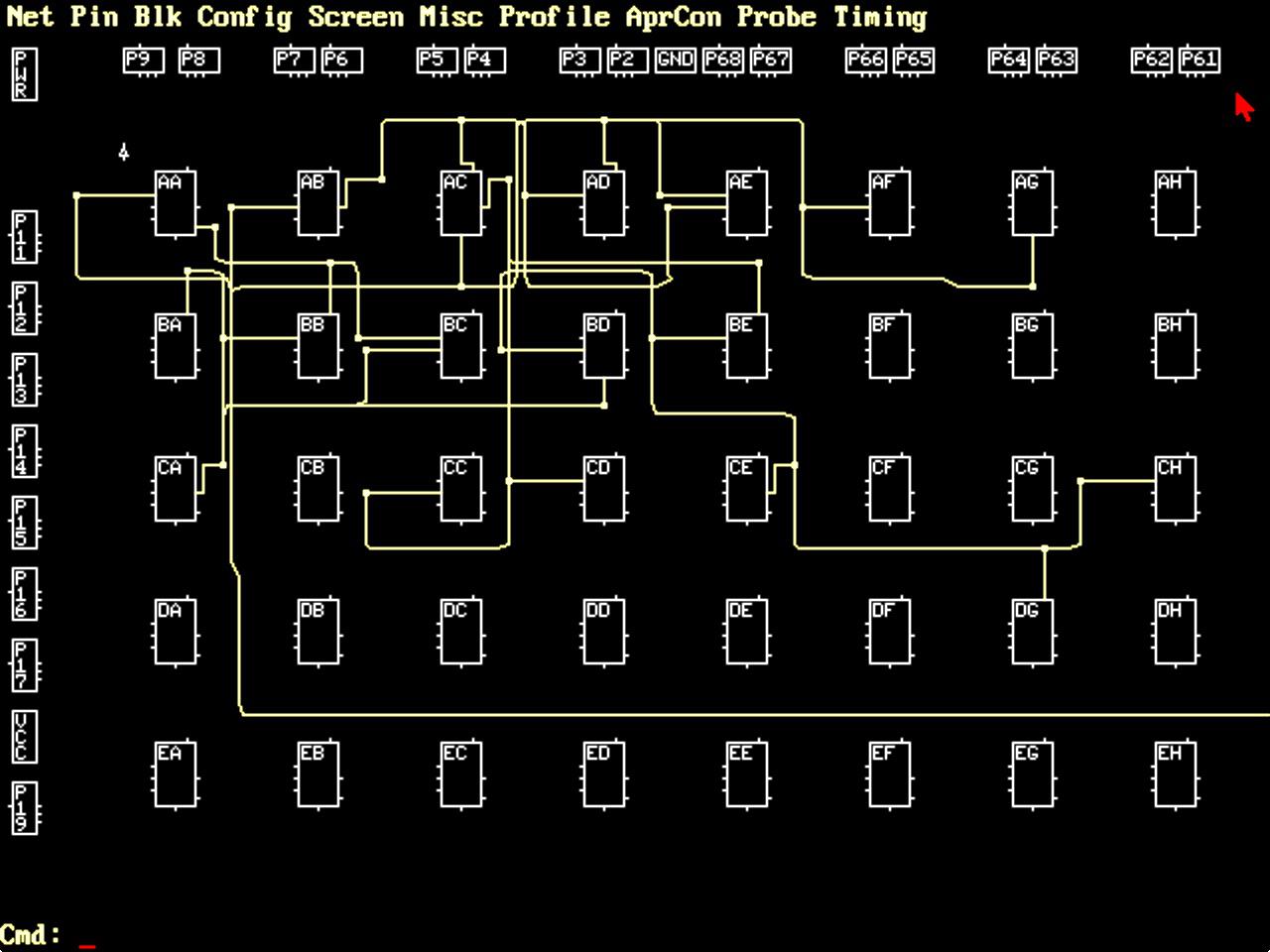

Das XC2064-FPGA verfügt über eine 8x8-CLB-Matrix. Jede CLB hat einen Namen von AA bis HH.

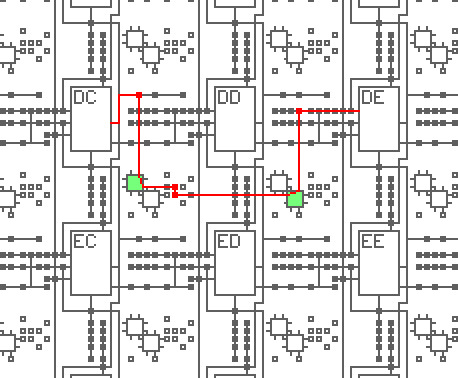

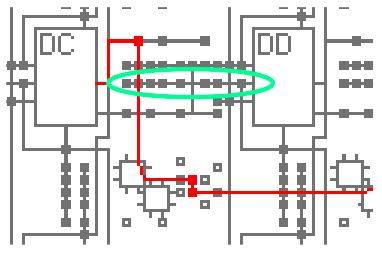

Die Verbindung kann beispielsweise den Ausgang eines DC-Blocks auf einen Eingang eines DE-Blocks umschalten, wie unten gezeigt. Die rote Linie zeigt den Signalweg und die kleinen roten Quadrate zeigen die aktivierten Verbindungspunkte. Beim Verlassen des DC-Blocks wird das Signal über einen 8-poligen Schalter (grün) zum ersten Verbindungspunkt geleitet, der es über zwei Verbindungspunkte und einen weiteren 8-Wege-Schalter (nicht verwendete vertikale und horizontale Leitungen nicht gezeigt) leitet. Beachten Sie, dass die Verbindung recht komplex ist, selbst bei einem so kurzen Pfad werden vier Verbindungspunkte und zwei Switches verwendet.

Beispiel für die Signalführung vom Ausgang eines DC-Blocks zu einem DE-Block.

Der folgende Screenshot zeigt, wie die Ablaufverfolgung in XACT erfolgt. Gelbe Linien zeigen Verbindungen zwischen logischen Blöcken. Mit zunehmender Anzahl von Signalen wird es schwierig, Verbindungen ohne Konflikte zwischen Pfaden herzustellen. XACT verfolgt automatisch, aber der Trace kann auch manuell bearbeitet werden.

Screenshot des XACT-Programms. Es ist ein MS-DOS-Programm und wird über Tastatur und Maus gesteuert.

Implementierung

Als nächstes betrachten wir die internen Schaltkreise des XC2064 durch Reverse Engineering anhand eines Fotos des Kristalls. Seien Sie gewarnt, dass dies eine gewisse Vertrautheit mit dem XC2064 erfordert.

Kristallfoto

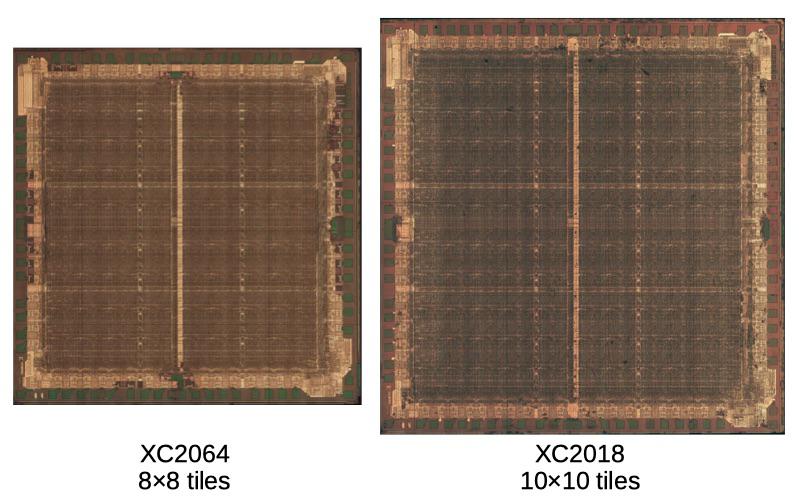

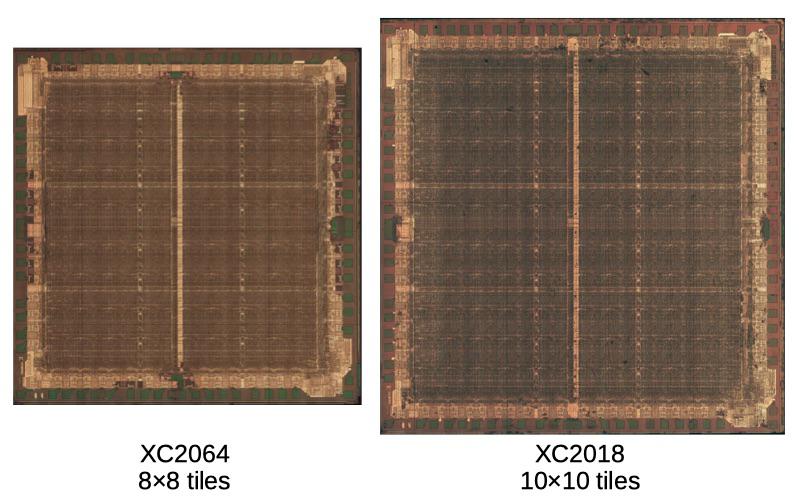

XC2064 XC20186, XC2064 XC2018 siliconpr0n. , . John McMaster , , . , .

XC2064 , John McMaster.

XC2064 , John McMaster.

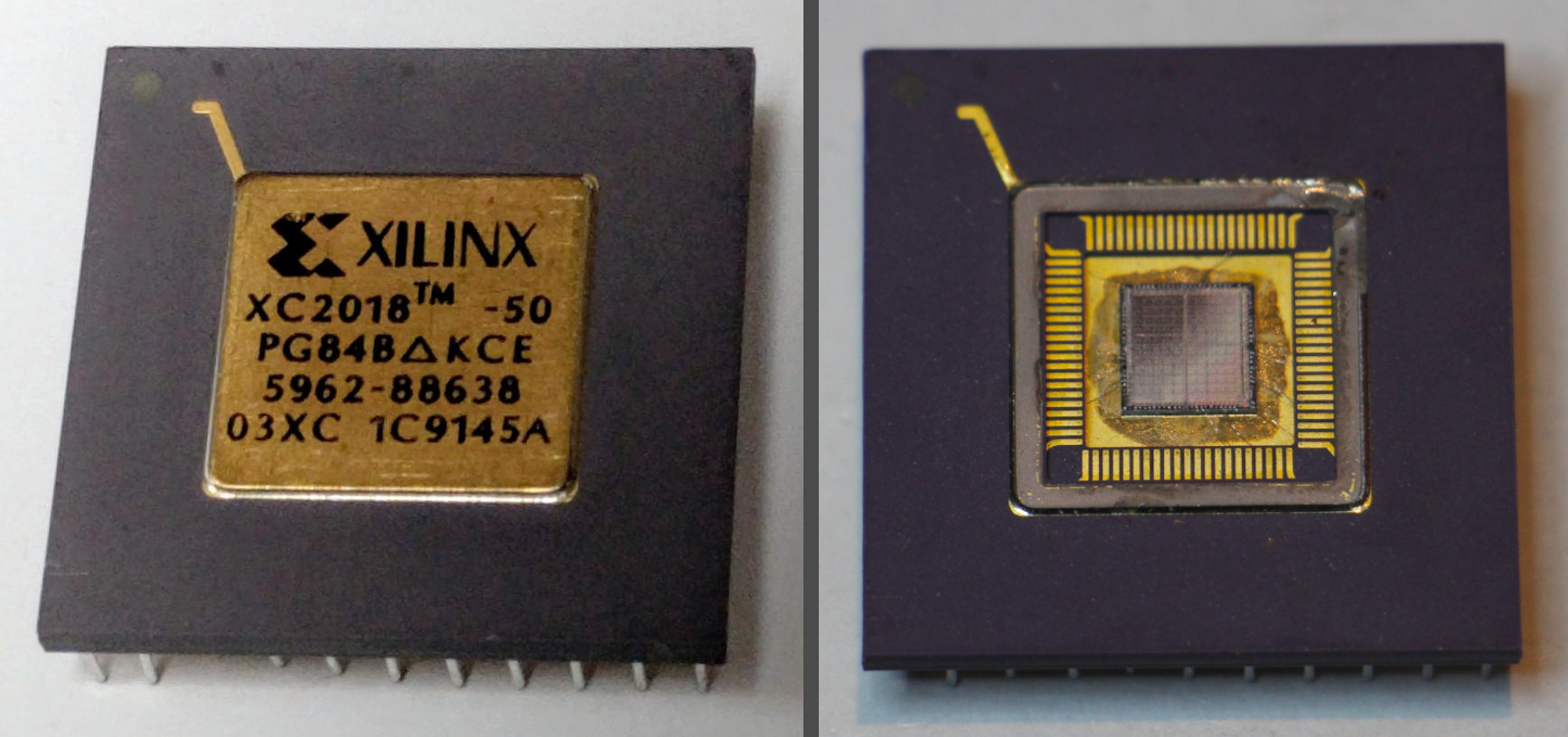

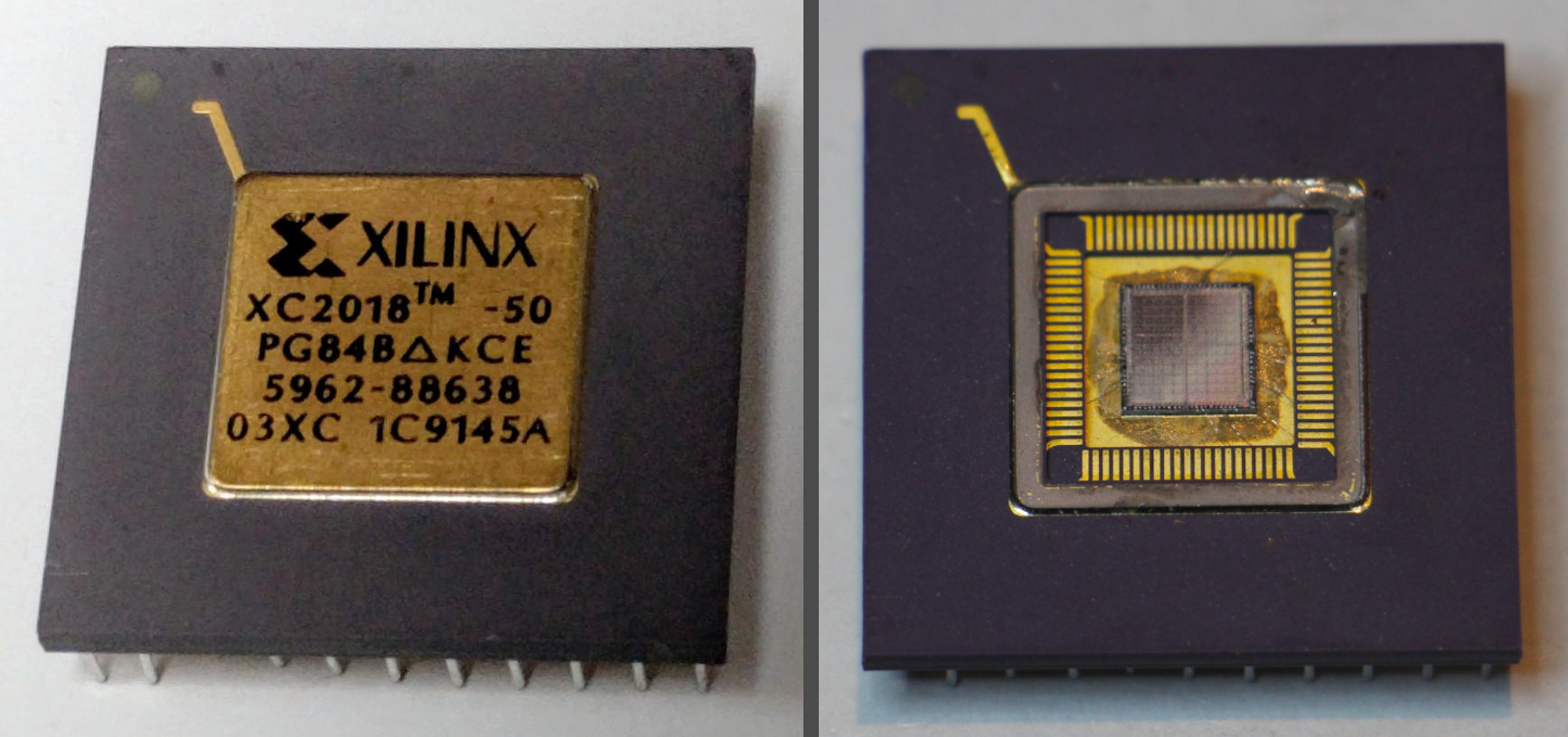

XC2018

Xilinx XC2018 ( ) 100 , , XC2064. , XC2064 64 , 1010, 88. XC2018 , .

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

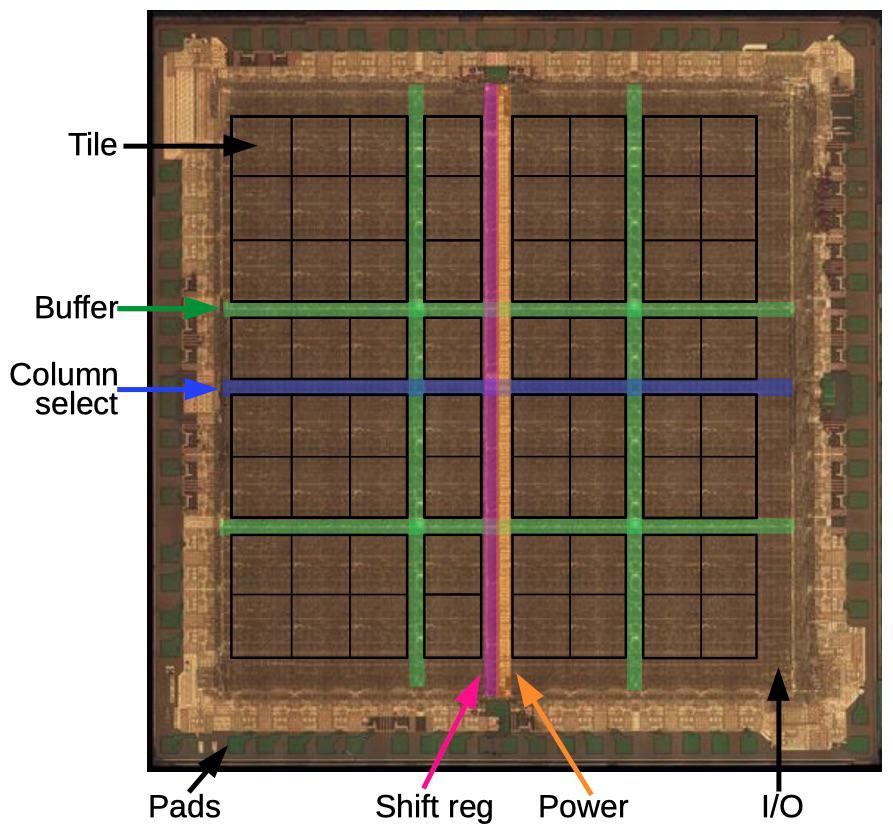

Unten sehen Sie ein Foto des XC2064-Kristalls. Der Hauptteil des FPGA besteht aus einer Matrix von 8 x 8 Blöcken, von denen jeder einen Logikblock und umgebende Schaltungen enthält. Obwohl das FPGA-Diagramm logische Blöcke (CLBs) getrennt von den Entity-Schaltplänen zeigt, ist dies in der Realität nicht der Fall. Tatsächlich ist jeder logische Block und seine Umgebung als ein einzelner Knoten, eine Kachel, implementiert. (Um genau zu sein, enthält die Kachel Verbindungen oben und links von jeder CLB.)

XC2064-Blocklayout. Entnommen von hier: siliconpr0n .

E / A-Blöcke befinden sich an den Seiten der integrierten Schaltung und ermöglichen die Kommunikation mit der Außenwelt. Sie sind mit den Stiften des Kristalls verbunden, die als kleine grüne Quadrate dargestellt sind, und mit den Stiften des Mikroschaltungsgehäuses verbunden. Auf dem Würfel befinden sich Puffer (grün): zwei vertikale und zwei horizontale. Diese Puffer verstärken das Signal, das sich über eine lange Strecke über den Chip bewegt, und verringern die Latenz. Das vertikale Schieberegister (pink) und die horizontale Spaltenabrufkette werden verwendet, um den Bitstrom in den Chip zu laden, wie unten gezeigt.

In den Fliesen

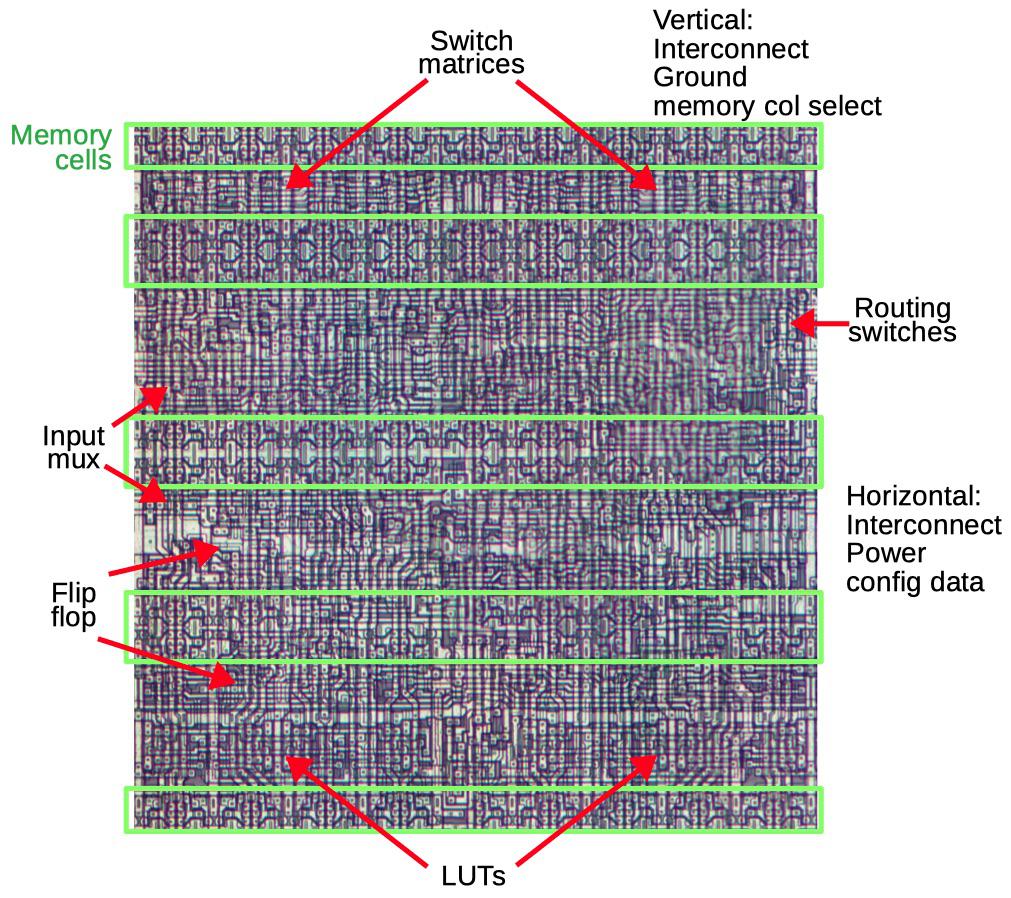

Die folgende Abbildung zeigt die Struktur einer XC2064-Kachel. Der Chip enthält 64 solcher Kacheln, die auf einem Chip gepackt sind. Etwa 40% jeder Kachel sind mit Speicherzellen (grün dargestellt) belegt, in denen Konfigurationsbits gespeichert sind. Das obere Drittel (ungefähr) der Kachel enthält die Verbindungsdiagramme: zwei Schaltermatrizen und eine Anzahl einzelner Verbindungsschalter. Unten ist der logische Block. Der Hauptteil des Logikblocks ist der Eingangsmultiplexer, das Flipflop und die Nachschlagetabelle. Die Kachel ist über horizontale und vertikale Kommunikationsleitungen mit den Nachbarn verbunden und auch mit den Strom- und Erdungsschienen. Die Konfigurationsdatenbits treten horizontal in die Speicherzellen ein, und die vertikalen Signale wählen eine bestimmte zu ladende Spalte aus.

Eine FPGA-Kachel mit wichtigen Funktionsknoten

Transistoren

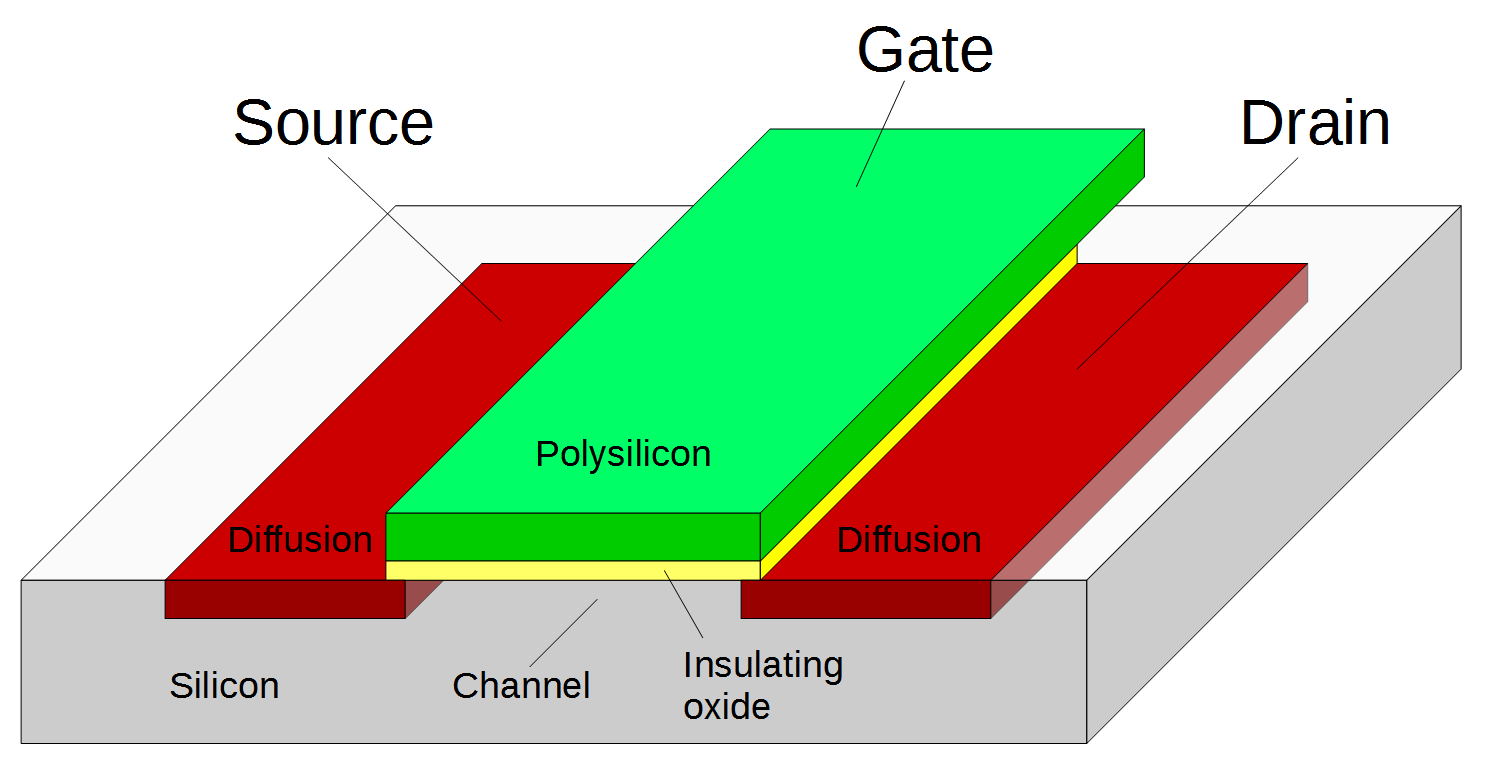

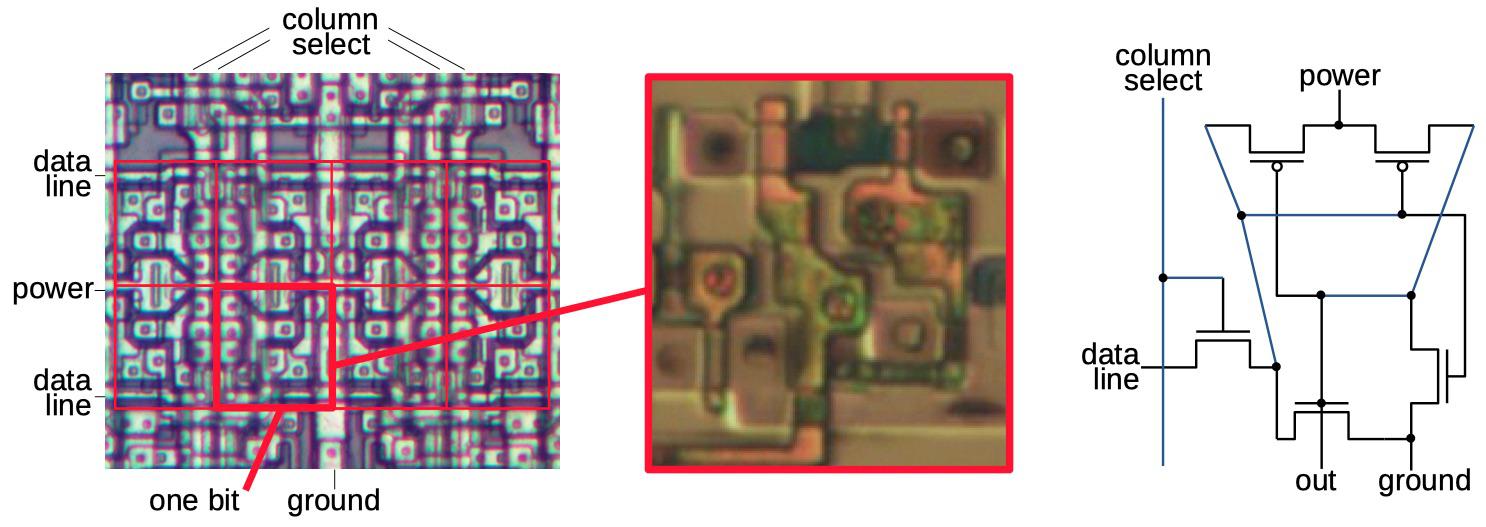

FPGA ist auf CMOS (CMOS) -Logik implementiert, die aus NMOS- und PMOS-Transistoren aufgebaut ist. Transistoren spielen in FPGAs zwei Hauptrollen. Zunächst werden logische Elemente aus ihren Kombinationen gebildet. Zweitens werden Transistoren als Schalter verwendet, durch die ein Signal beispielsweise geleitet wird, um Verbindungen zwischen Blöcken herzustellen. Ein Transistor, der diese Rolle übernimmt, wird als Durchgangstransistor bezeichnet. Die folgende Abbildung zeigt die Grundstruktur eines MOSFET. Zwei Siliziumabschnitte sind mit Verunreinigungen dotiert, um einen Drain und eine Source zu erzeugen. Zwischen ihnen befindet sich ein Gate, das den Transistor ein- und ausschaltet und den Strom zwischen Drain und Source steuert. Der Verschluss besteht aus einem speziellen Siliziumtyp namens Polysilizium, der durch eine dünne Oxidschicht vom darunter liegenden Silizium isoliert ist. Darüber befinden sich zwei Metallisierungsschichten, die Schaltungsverbindungen bereitstellen.

MOSFET-Struktur

Auf dem Foto des Kristalls können wir beobachten, wie der Transistor unter einem Mikroskop aussieht. Das Polysilicium-Gate ist eine Serpentinenlinie zwischen zwei dotierten Siliziumbereichen. Die Kreise sind Durchkontaktierungen, die das Silizium und die Metallschicht verbinden (die auf diesem Foto entfernt wird).

FPGA-MOSFET

Bitstream und Konfigurationsspeicher

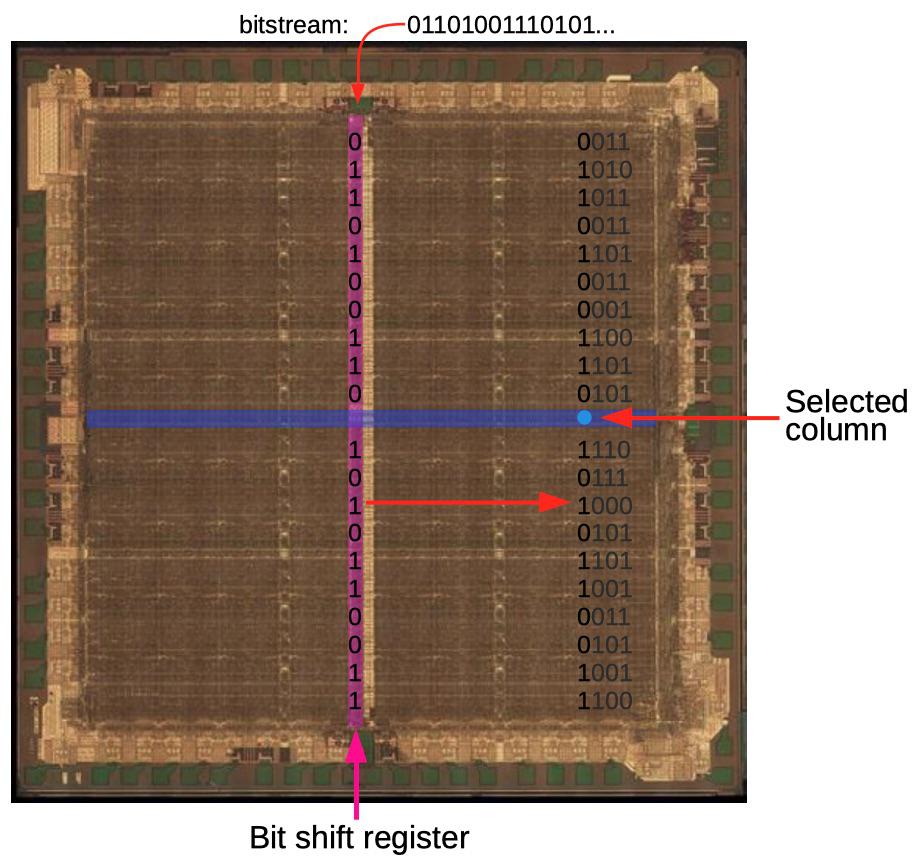

Die Konfigurationsinformationen im XC2064 werden in den Konfigurationsspeicherorten gespeichert. Das FPGA verwendet hierfür keinen Blockspeicher. Stattdessen wird der Konfigurationsspeicher in Form eines 160 x 71-Gitters im gesamten Kristall verteilt. Jedes Bit wird neben der von ihm gesteuerten Schaltung platziert. Die folgende Abbildung zeigt den in das FPGA geladenen Konfigurationsbitstrom. Der Bitstrom wird in das Schieberegister geladen, das sich in der Mitte des Chips befindet (rosa). Sobald 71 Bits in das Schieberegister geladen sind, wählt die Spaltenabrufschaltung (blau) die gewünschte Speicherspalte aus und die Bits werden parallel in die Spalte geladen. Dann werden die nächsten 71 Bits in das Schieberegister geladen und die nächste Spalte links ausgewählt. Der Vorgang wird für alle 160 Spalten des FPGA wiederholt, und der gesamte Bitstrom wird in das FPGA geladen. Die Verwendung eines Schieberegisters macht große Speicheradressierungsschaltungen überflüssig.

Wie der Bitstrom in das FPGA geladen wird. Bits werden herkömmlicherweise gezeigt, die tatsächliche Speicherung von Bits ist viel dichter. Die drei Spalten rechts wurden bereits geladen und die vierte wird geladen. Das Foto des Kristalls stammt von hier: siliciumpr0n .

Wichtig ist, dass der Bitstrom genau in der Reihenfolge über den Chip verteilt ist, in der die Bits in der Datei erscheinen: Die Packung der Bits im Bitstrom entspricht ihrer physischen Platzierung auf dem Chip. Wie unten gezeigt wird, wird jedes Bit im FPGA neben der von ihm gesteuerten Schaltung gespeichert. Somit wird das Bitstream-Dateiformat direkt durch die Platzierung der Hardwareschaltungen bestimmt. Wenn beispielsweise zwischen den Kacheln eine Lücke besteht und sich ein Puffer darin befindet, befindet sich dieselbe Lücke im Bitstrom. Die Struktur des Bitstroms hängt nicht von Software-Abstraktionen wie Feldern in Datentabellen oder Konfigurationsblöcken ab. Um Bitstream zu verstehen, muss man in Hardware und nicht in Software denken

Bitstream

, (.RBT) , .

, .

, .

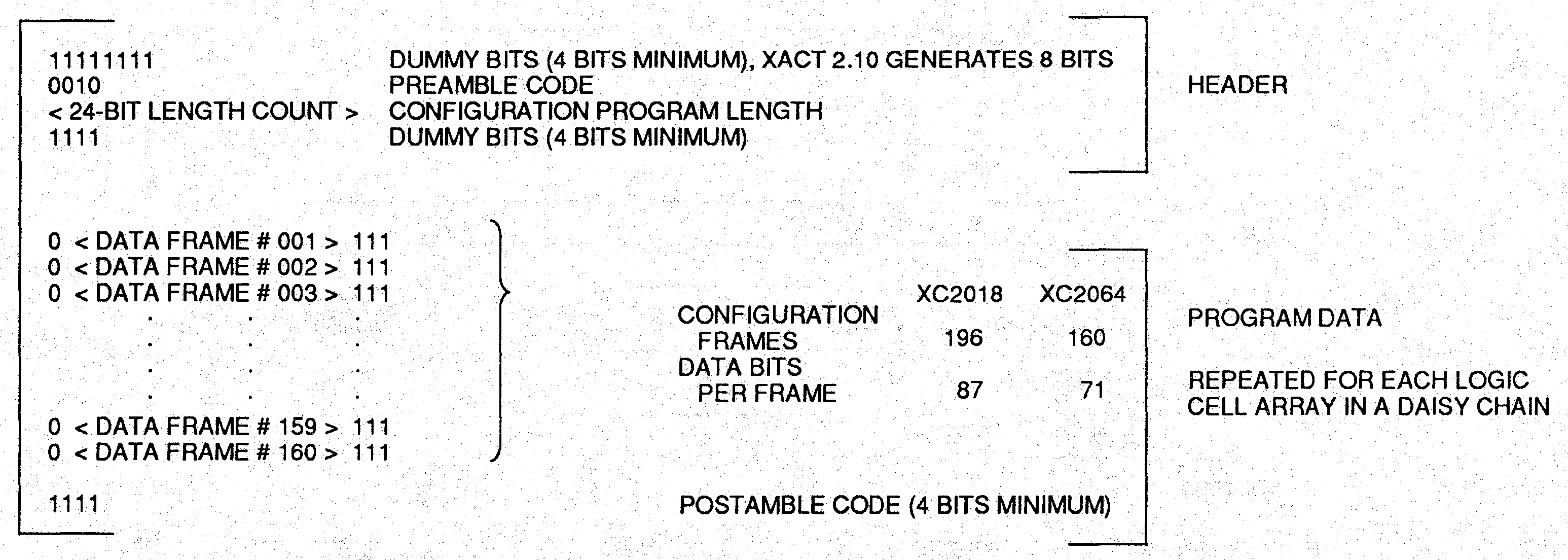

Jedes Bit des Konfigurationsspeichers wird wie unten gezeigt implementiert. Jede Speicherzelle besteht aus zwei Wechselrichtern, die in einer Schleife verbunden sind. Eine solche Schaltung hat zwei stabile Zustände und kann ein Bit speichern: Entweder befindet sich der obere Wechselrichter im Zustand 1 und der untere Wechselrichter im Zustand 0 oder umgekehrt. Um in die Zelle zu schreiben, wird der linke Durchgangstransistor aktiviert, der das Signal weiterleitet. Das Signal auf der Datenleitung zieht einfach den Wechselrichter und schreibt das erforderliche Bit. (Sie können die Konfigurationsdaten auch mit demselben Strompfad lesen.) Ausgang Q und invertiertes Q steuern eine bestimmte Funktion im FPGA, z. B. das Schließen einer Verbindung, das Abrufen eines Bits aus einer Nachschlagetabelle oder das Steuern eines Triggers. In den meisten Fällen wird nur der Q-Ausgang verwendet.

SRAM-Zelle

(SRAM). , RAM, , , SRAM. , 5T SRAM.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

Diagramm eines Bits Konfigurationsspeicher aus der Dokumentation.

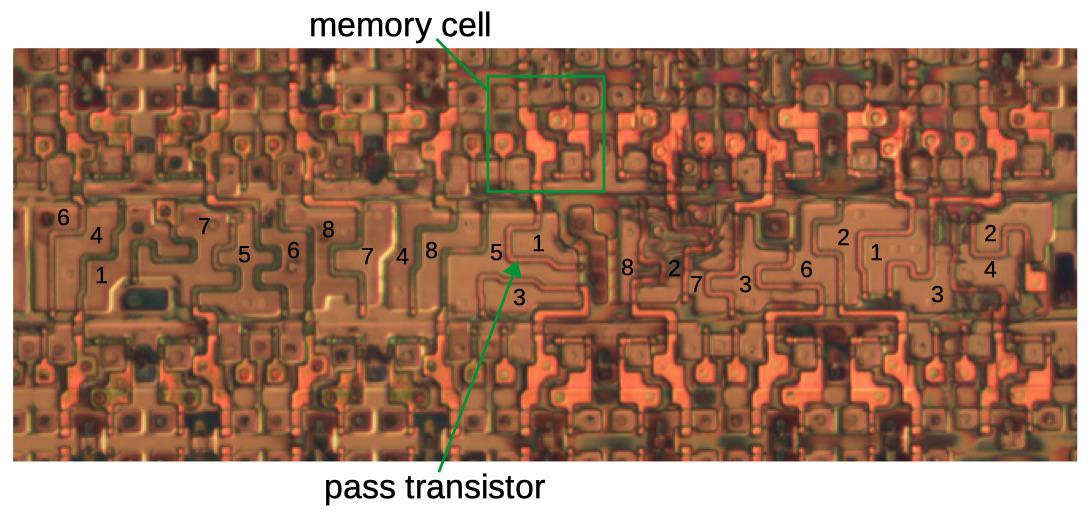

Die folgende Abbildung zeigt die physikalische Struktur von Speicherzellen. Das Foto links zeigt 8 Speicherzellen, von denen eine hervorgehoben ist. Jede horizontale Datenleitung ist mit allen Speicherplätzen in der Zeile verbunden. Jede Spaltenabrufzeile wählt alle Speicherorte in der Spalte aus und ermöglicht so das Schreiben. Das mittlere Foto zeigt Abschnitte aus Silizium und Polysilizium für eine Speicherzelle. Die Metallschichten wurden entfernt, um die darunter liegenden Transistoren freizulegen. Metallisierungsschichten verbinden Transistoren, Kreise auf dem Foto, dies sind Verbindungen, Durchkontaktierungen zwischen Silizium oder Polysilizium und Metall. Das Diagramm zeigt, wie fünf Transistoren verbunden sind. Die Platzierung der Elemente im Diagramm entspricht ihrer Platzierung auf dem Foto. Zwei Transistorpaare bilden die CMOS-Inverter, wobei unten links ein Durchgangstransistor den Zugang zur Zelle ermöglicht.

, . — . , . . : siliconpr0n.

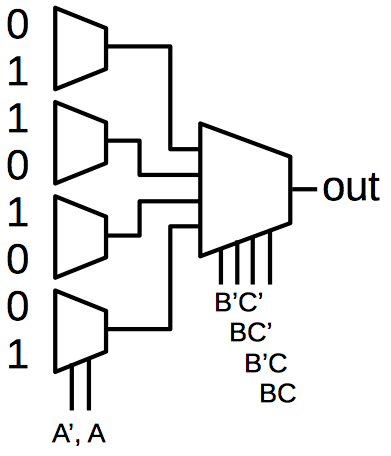

Wie bereits erläutert, implementiert FPGA beliebige Logikfunktionen mithilfe von Nachschlagetabellen. Die folgende Abbildung zeigt, wie die Nachschlagetabelle in XC2064 implementiert ist. Die acht Werte links werden an acht Speicherplätzen gespeichert. Vier Multiplexer wählen abhängig von dem Wert am Eingang A eines von jedem Wertepaar aus. Wenn A = 0 ist, wird der obere der Werte ausgewählt, wenn A = 1, dann der untere. Dann wählt der große Multiplexer einen von vier Werten basierend auf den Signalen B und C. Das Ergebnis ist ein bestimmter Wert, in diesem Fall A XOR B XOR C. Wir können jede Logikfunktion ausführen, indem wir verschiedene Werte in der Tabelle einsetzen.

XOR-Implementierung in der Nachschlagetabelle.

Jeder Multiplexer wird unter Verwendung von Durchgangstransistoren implementiert. Abhängig von den Steuersignalen wird einer der Durchgangstransistoren aktiviert, der Daten von Eingang zu Ausgang weiterleitet. Die folgende Abbildung zeigt einen Teil der LUT-Kette mit zwei gemultiplexten Bits. Auf der rechten Seite befinden sich zwei Speicherplätze. Jedes Bit wird durch den Inverter geleitet, verstärkt und durch die Durchgangstransistoren des Multiplexers in der Mitte geleitet, wobei eines dieser Bits ausgewählt wird.

Ansicht der Netze, die die LUT implementieren. Entnommen aus siliciumpr0n.

Auslösen

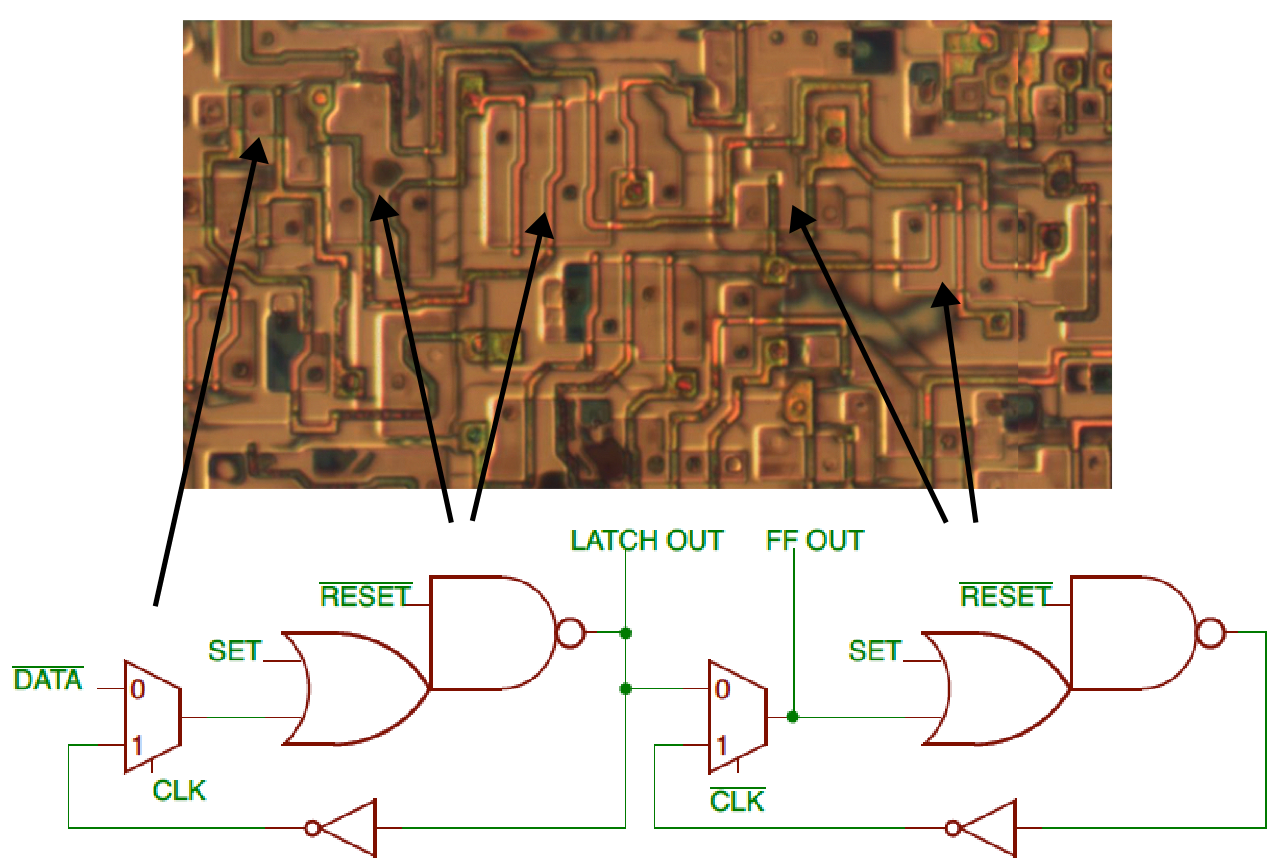

Jede CLB enthält ein Flip-Flop, mit dem das FPGA Latches, Zustandsautomaten und andere zustandsbehaftete Netze implementieren kann. Die folgende Abbildung zeigt eine (etwas ungewöhnliche) Trigger-Implementierung. Sie verwendet das folgende Schema. Wenn das Taktsignal Null ist, leitet der erste Multiplexer Daten an den ersten Latch weiter, der den Wert speichert. Das Bit wird beim Durchgang durch die ODER-, NAND- und Inverter-Gatter zweimal invertiert und bleibt daher gleich. Ferner empfängt der zweite Latch-Multiplexer das Bit vom ersten Latch, wenn der Takt auf 1 steigt (beachten Sie, dass der Takt invertiert ist). Dieser Wert ist der Ausgang des Flip-Flops. Wenn das Taktsignal auf 0 gesetzt ist, schließt der sekundäre Multiplexer die Schleife durch Zwischenspeichern des Bits. Somit ist der Trigger empfindlich gegenüber der Flanke des Signals,Verriegeln des Wertes an der Vorderflanke des Taktsignals. Setzen und Zurücksetzen von Linien Setzen und Zurücksetzen des Flip-Flops.

. OR-NAND : siliconpr0n.

Die Schaltmatrix ist ein wichtiges Verbindungselement. Jeder Schalter hat 8 Pins (zwei auf jeder Seite) und kann sie auf nahezu jede Weise verbinden. Signale können flexibler als an einzelnen Verbindungsknoten entpackt, aufgeteilt und geschnitten werden. Die folgende Abbildung zeigt einen Teil des Verbindungsnetzwerks zwischen den vier CLBs (blau). Schaltmatrizen (grün) können in beliebiger Kombination von Verbindungen auf der rechten Seite angeschlossen werden. Beachten Sie, dass jeder Stift in einer Menge von 5 bis 7 Stück mit anderen Stiften verbunden werden kann. Zum Beispiel kann Pin 1 mit Pin 3 verbunden werden, nicht jedoch mit Pin 2 und 4. Dies macht die Matrix mit 20 möglichen Verbindungen anstelle von 28 nahezu vollständig.

Von hier aus: Xilinx Programmable Gate Array Data Book , Abb. 7b.

Die Schaltmatrix wird durch Reihen von Durchgangstransistoren gebildet, die von den Speicherzellen über und unter ihnen gesteuert werden. Die zwei Seiten des Transistors sind zwei Stifte der Schaltmatrix, die durch den Transistor verbunden werden können. Jede Matrix hat also 20 Steuerbits, zwei Matrizen pro Kachel ergeben 40 Bits pro Kachel. Das Foto unten zeigt eine Speicherzelle, die mit dem Wellentor des darunter liegenden Durchgangstransistors verbunden ist. Dieser Transistor stellt die Verbindung zwischen Pin 5 und Pin 1 bereit. Somit steuert das Bit in dem Bitstrom, das diesem Speicherort entspricht, die Verbindung zwischen Pin 5 und 1. In ähnlicher Weise steuern andere Speicherzellen und ihre zugehörigen Transistoren andere Verbindungen. Beachten Sie auch, dass die Reihenfolge dieser Verbindungen keinem bestimmten Muster folgt.Die Entsprechung zwischen den Bits im Bitstrom und den Schaltstiften sieht zufällig aus.

Matrix wechseln

20 . 18 , .

Implementierung einer 8-Kanal-Verbindungsmatrix. Die Siliziumbereiche sind durch die Anzahl ihrer entsprechenden Stifte gekennzeichnet. Die Metallschichten, die die entsprechenden Leitungen mit den Transistoren verbinden, wurden entfernt. Entnommen aus siliciumpr0n.

Eingangsanschlüsse

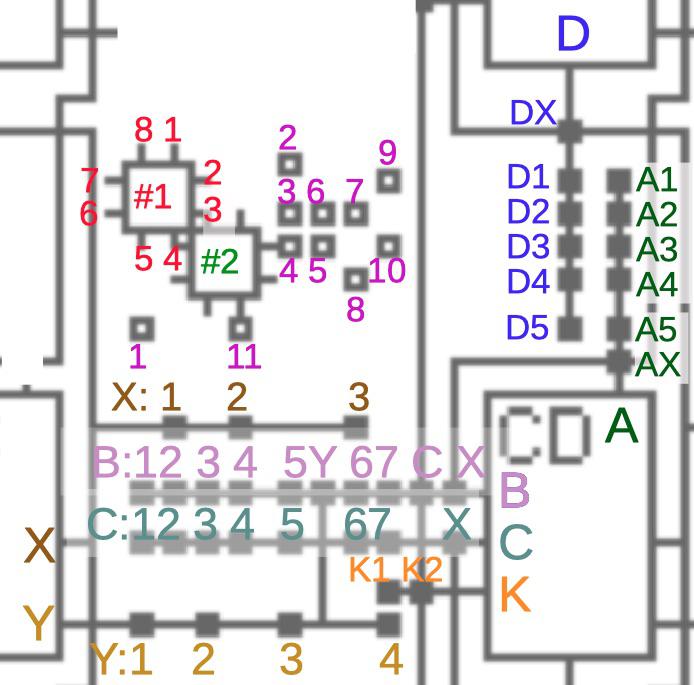

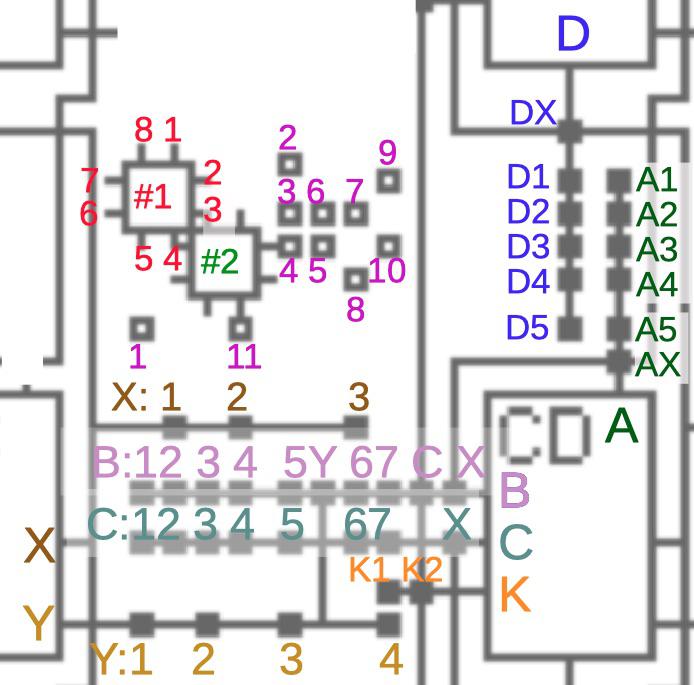

CLB-Eingänge verwenden ein anderes Bitstrom-Codierungsschema, was durch die Hardware-Implementierung erklärt wird. In der Abbildung unten sind die acht Ellipsenknoten potenzielle Eingaben in die CLB mit der Bezeichnung DD. Es kann nur ein Knoten (maximal) als Eingang konfiguriert werden, da durch das Verbinden von zwei Signalen mit einem Eingang diese kurzgeschlossen werden können.

Eingangsauswahl. Die acht grün eingekreisten Eingänge sind potenzielle DD-Eingänge, von denen nur einer ausgewählt werden kann.

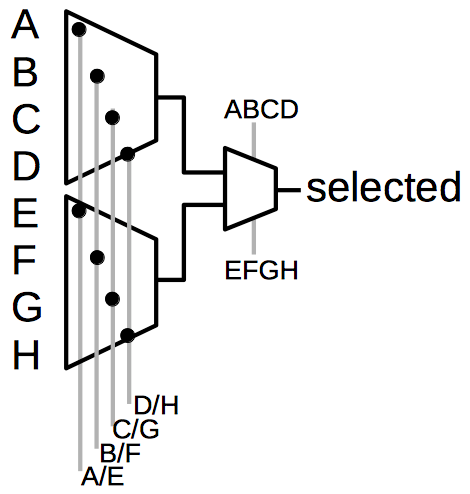

Der gewünschte Eingang wird vom Multiplexer ausgewählt. Eine einfache Lösung wäre die Verwendung eines Multiplexers mit 8 Eingängen und drei Steuerbits, die eines von 8 Signalen auswählen. Eine andere einfache Lösung wäre die Verwendung von 8 Durchgangstransistoren mit jeweils einem eigenen Steuersignal, von denen einer das erforderliche Signal auswählt. Das FPGA verwendet jedoch einen Hybridansatz, der im ersten Fall die Notwendigkeit eines Decoders beseitigt, jedoch 5 Steuersignale anstelle der 8 im zweiten Ansatz erforderlichen erfordert.

Das FPGA verwendet Multiplexer, um einen von acht Eingängen auszuwählen.

Das Diagramm in der obigen Abbildung zeigt den im FPGA verwendeten Zweischichtmultiplexer. In der ersten Stufe wird eines der Steuersignale aktiviert. In der zweiten Stufe wird das hohe oder niedrige Signal ausgewählt und an den Ausgang angelegt. Angenommen, das Steuersignal B / F wird an die erste Stufe und ABCD an die zweite Stufe angelegt. Eingang B ist der einzige, der an den Ausgang geht. Das heißt, die Auswahl eines der acht Eingänge erfordert 5 Bits im Bitstrom und verwendet 5 Speicherplätze.

Eingangsmultiplexer CLB

CLB. EFGH ABCD, . -, CLB 6 10 , , . , , , , . , , 6 , . , , .

Fazit

Der XC2064 verwendet eine Vielzahl hochoptimierter Netze, um Logikblöcke und Netzverbindungen zu implementieren. Diese Ketten müssen dicht gepackt sein, um in den Kristall zu passen. Trotzdem war der XC2064 ein sehr großer Chip, größer als der damalige Mikroprozessor und schwer herzustellen, was Hunderte von Dollar kostete. Im Vergleich zu modernen FPGAs hat der XC2064 eine absurd kleine Anzahl von Zellen, aber selbst das war der Beginn einer revolutionären neuen Produktlinie.

Zwei Konzepte sind der Schlüssel zum Verständnis des XC2064-Bitstroms. Zunächst wird das FPGA auf der Basis von 64 Kacheln implementiert, wobei Blöcke wiederholt werden, die logische Blöcke und Verbindungen kombinieren. Obwohl beschrieben wird, dass das FPGA Logikblöcke aufweist, die von Verbindungen umgeben sind, wird es nicht auf diese Weise implementiert. Das zweite Konzept ist, dass der Bitstrom nicht auf Abstraktionen basiert, sondern die zweidimensionale Packung von FPGA-Speicherzellen direkt abbildet. Daher ist Bitstream nur dann sinnvoll, wenn Sie die physische Struktur des FPGA berücksichtigen.

Hinweis

, XC2064 (. 11), CLB . , , 20% , . — -, . , . .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

Ich habe meinen letzten Beitrag auf Twitter angekündigt, also folge kenshirriff . Ich habe auch einen RSS-Feed . Vielen Dank an John McMaster, Tim Ansell und Philip Freidin für die Diskussionen.