Alle Zentraleinheiten eines Computers, sei es ein billiger Laptop oder ein Server für Millionen von Dollar, haben ein Gerät, das als Cache bezeichnet wird. Und mit sehr hoher Wahrscheinlichkeit hat es mehrere Ebenen.

Es ist wahrscheinlich wichtig, sonst warum es installieren? Aber was macht der Cache und warum hat er verschiedene Ebenen? Und was bedeutet "12-Wege-Satzassoziativ"?

Was ist Cache?

TL; DR: Dies ist ein kleiner, aber sehr schneller Speicher, der sich in unmittelbarer Nähe der logischen Blöcke der CPU befindet.

Natürlich können wir viel mehr über den Cache erfahren ...

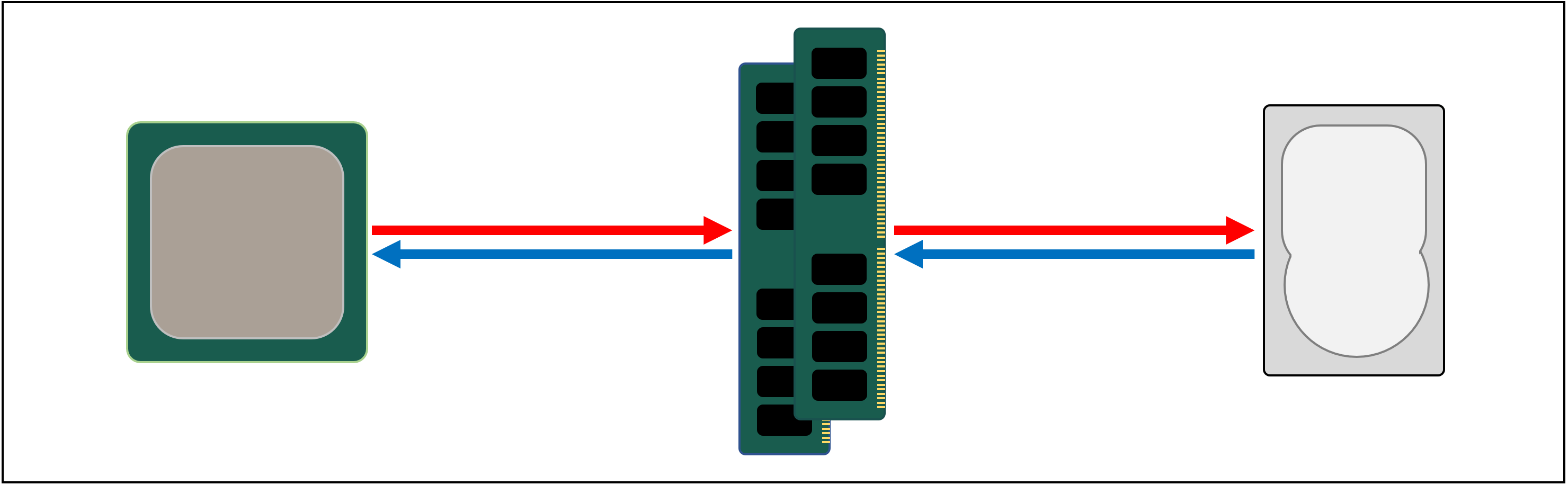

Beginnen wir mit einem imaginären magischen Speichersystem: Es ist unendlich schnell, kann unendlich viele Datenübertragungen gleichzeitig verarbeiten und bietet immer eine zuverlässige und sichere Datenspeicherung. Natürlich gibt es nichts dergleichen in der Nähe, aber wenn dies so wäre, wäre die Struktur des Prozessors viel einfacher.

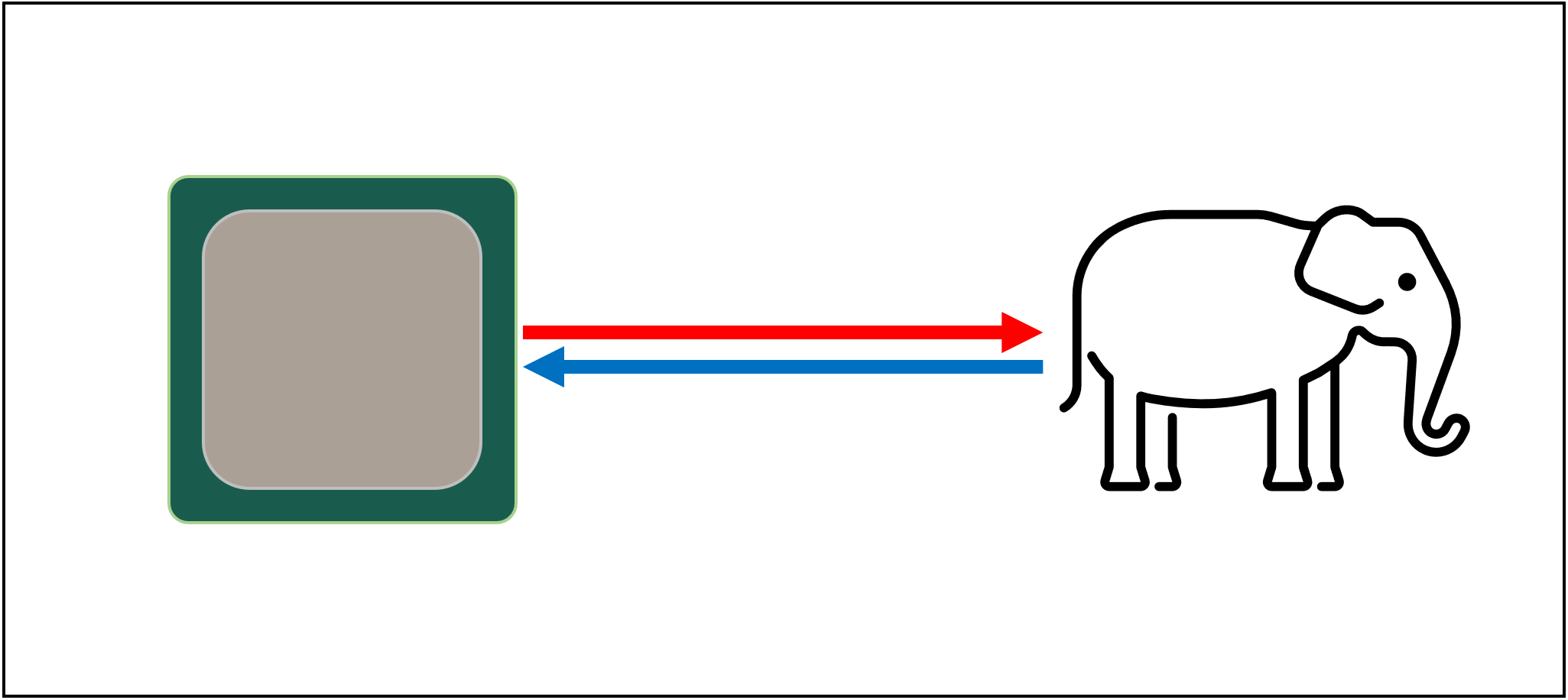

Prozessoren würden dann nur logische Blöcke zum Addieren, Multiplizieren usw. sowie ein Datenübertragungssteuersystem benötigen, da unser theoretisches Speichersystem in der Lage ist, alle erforderlichen Zahlen sofort zu senden und zu empfangen; Kein Logikblock muss im Leerlauf stehen, während auf die Datenübertragung gewartet wird.

Aber wie wir wissen, gibt es keine solche magische Speichertechnologie. Stattdessen haben wir Festplatten oder Solid-State-Laufwerke, und selbst die besten von ihnen entsprechen nicht den Verarbeitungskapazitäten, die ein moderner Prozessor benötigt.

Das große T'Fon des Speichers

Der Grund dafür ist, dass moderne Prozessoren unglaublich schnell sind - sie benötigen nur einen Taktzyklus, um zwei 64-Bit-Ganzzahlen hinzuzufügen. Wenn der Prozessor mit 4 GHz läuft, sind dies nur 0,00000000025 Sekunden oder eine Viertelnanosekunde.

Gleichzeitig benötigt eine sich drehende Festplatte Tausende von Nanosekunden, um Daten auf den Festplatten zu finden, ganz zu schweigen von deren Übertragung, und Solid-State-Laufwerke benötigen zehn oder Hunderte von Nanosekunden.

Offensichtlich können solche Antriebe nicht gebaut werden innenProzessoren, so wird es eine physische Trennung zwischen ihnen geben. Daher wird Zeit zum Verschieben von Daten hinzugefügt, was die Situation verschärft.

Leider ist dies die große A'Tuin der Datenspeicherung.

Deshalb benötigen wir ein anderes Speichersystem zwischen dem Prozessor und dem Hauptlaufwerk. Es sollte schneller als ein Speichergerät sein, mehrere Datenübertragungen gleichzeitig verarbeiten können und viel näher am Prozessor liegen.

Nun, wir haben bereits ein solches System und es heißt RAM . Es ist in jedem Computer vorhanden und führt genau diese Aufgabe aus.

Fast alle derartigen Speicher sind vom DRAM- Typ (Dynamic Random Access Memory) . Sie können Daten viel schneller übertragen als jedes andere Speichergerät.

Trotz seiner enormen Geschwindigkeit ist DRAM nicht in der Lage, solche Datenmengen zu speichern.

Einige der größten von Micron entwickelten DDR4-Speicherchips speichern 32 GB oder 4 GB Daten. Die größten Festplatten speichern 4.000 Mal mehr.

Obwohl wir die Geschwindigkeit unseres Datennetzwerks erhöht haben, benötigen wir zusätzliche Systeme (Hardware und Software), um herauszufinden, welche Daten in einer begrenzten Menge DRAM gespeichert werden sollen, die vom Prozessor verarbeitet werden kann.

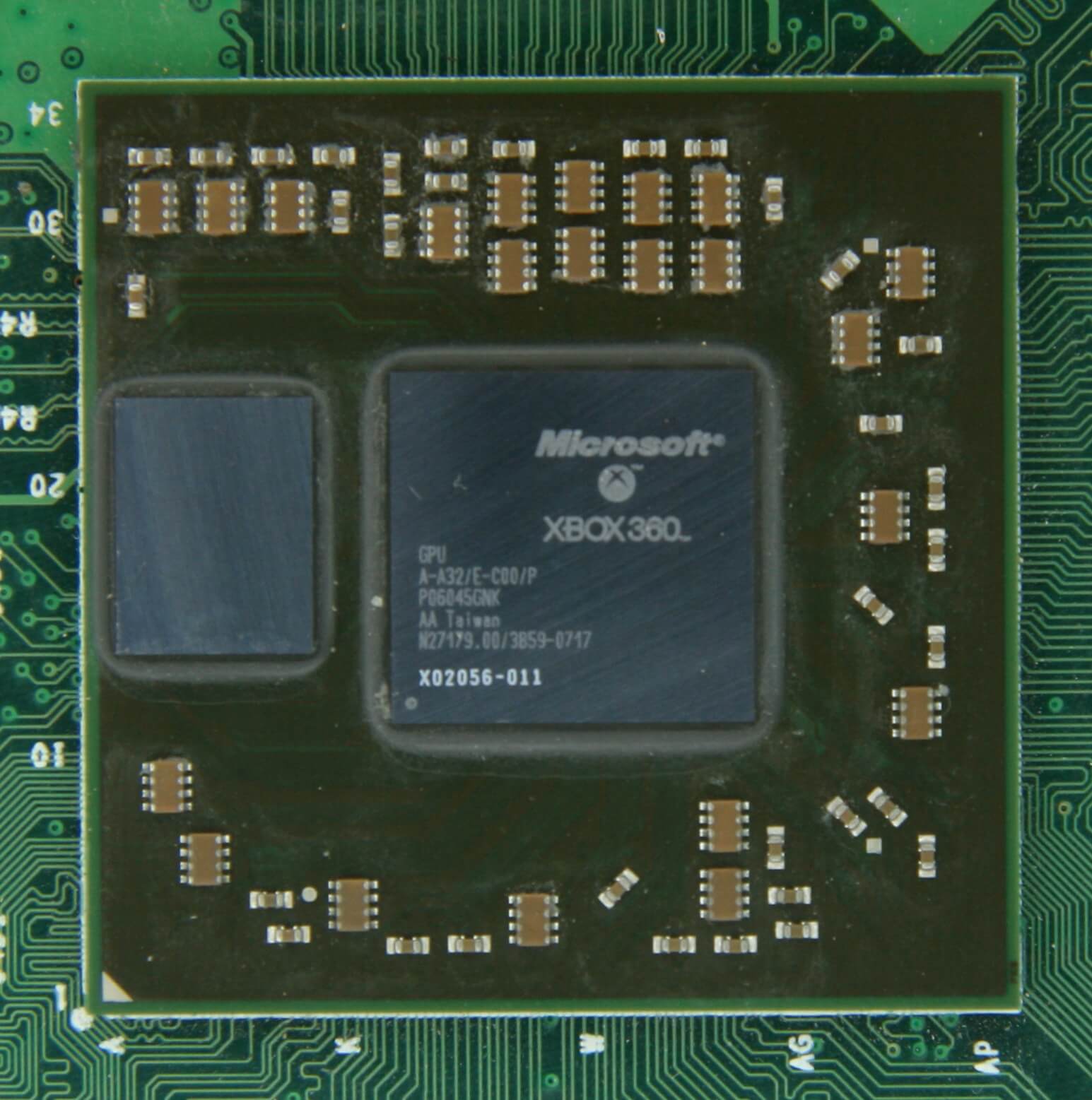

DRAM kann in einem Chip-Paket hergestellt werden (dies wird als eingebetteter DRAM bezeichnet). Prozessoren sind jedoch recht klein, sodass sie nicht viel Speicherplatz bieten.

10 MB DRAM links von der Xbox 360-GPU. Quelle: CPU Grave Yard

Die überwiegende Mehrheit des DRAM befindet sich in unmittelbarer Nähe des Prozessors, ist mit dem Motherboard verbunden und ist immer die Komponente, die dem Prozessor am nächsten liegt. Dieser Speicher ist jedoch immer noch nicht schnell genug ...

DRAM benötigt ungefähr 100 Nanosekunden, um Daten zu finden, kann aber zumindest Milliarden von Bits pro Sekunde übertragen. Es sieht so aus, als bräuchten wir eine weitere Speicherstufe, die zwischen den CPU- und DRAM-Blöcken platziert werden kann.

Die verbleibende Stufe erscheint in der Szene: SRAM ( statischer Direktzugriffsspeicher)). DRAM verwendet mikroskopische Kondensatoren, um Daten in Form einer elektrischen Ladung zu speichern, während SRAM Transistoren für dieselbe Aufgabe verwendet, die mit derselben Geschwindigkeit wie die logischen Blöcke des Prozessors arbeiten (ungefähr 10-mal schneller als DRAM).

Natürlich hat SRAM einen Nachteil, und wieder hat es mit Platz zu tun.

Der Transistorspeicher nimmt viel mehr Platz ein als der DRAM: In der gleichen Größe wie ein 4 GB DDR4-Chip können Sie weniger als 100 MB SRAM erhalten. Da es jedoch nach demselben Herstellungsverfahren wie die CPU hergestellt wird, kann der SRAM direkt in den Prozessor eingebettet werden, so nah wie möglich an den logischen Blöcken.

Mit jedem weiteren Schritt haben wir die Geschwindigkeit der übertragenen Daten auf Kosten des gespeicherten Volumes erhöht. Wir können fortfahren und neue Schritte hinzufügen, die schneller, aber kleiner sein werden.

Und so kamen wir zu einer strengeren DefinitionCache-Konzepte: eine Sammlung von SRAMs im Prozessor; Sie maximieren die Prozessorauslastung, indem sie Daten mit sehr hohen Geschwindigkeiten übertragen und speichern. Sind Sie mit dieser Definition zufrieden? Großartig, denn von nun an wird alles viel komplizierter!

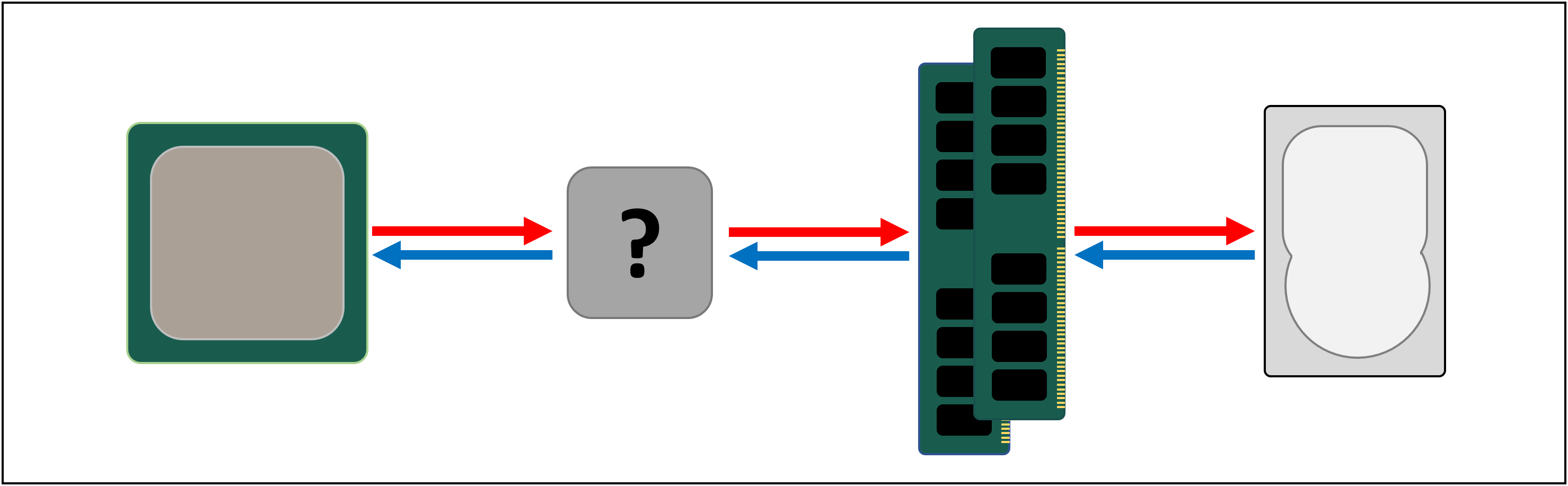

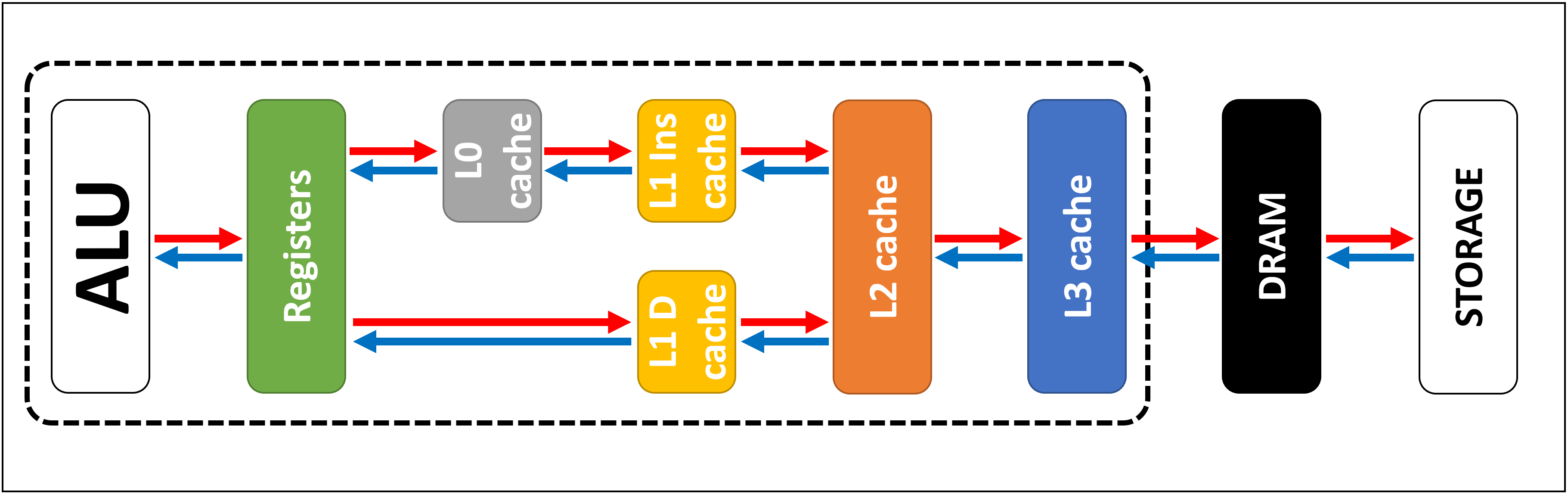

Bargeld: Parkhaus auf mehreren Ebenen

Wie oben erwähnt, ist der Cache erforderlich, da wir kein magisches Speichersystem haben, das den Datenverbrauch logischer Blöcke des Prozessors verarbeiten kann. Moderne CPUs und GPUs enthalten viele SRAMs, die in einer Hierarchie angeordnet sind - eine Folge von Caches mit der folgenden Struktur:

In der obigen Abbildung ist der Prozessor (CPU) durch ein gestricheltes Rechteck gekennzeichnet. Links sind ALUs (arithmetische Logikeinheiten); Dies sind Strukturen, die mathematische Operationen ausführen. Obwohl es sich nicht ausschließlich um einen Cache handelt, sind die Register die nächstgelegene Speicherebene zur ALU (sie sind in einer Registerdatei angeordnet ).

Jeder von ihnen speichert eine Zahl, beispielsweise eine 64-Bit-Ganzzahl. Der Wert selbst kann ein Element einiger Daten, ein Code eines bestimmten Befehls oder eine Speicheradresse einiger anderer Daten sein.

Die Registerdatei in Desktop-Prozessoren ist beispielsweise in jedem der Intel Core i9-9900K-Kerne recht kleinEs gibt zwei Bänke solcher Dateien, und die für Ganzzahlen enthält nur 180 64-Bit-Ganzzahlen. Eine andere Registerdatei für Vektoren (kleine Arrays von Zahlen) enthält 168 256-Bit-Elemente. Das heißt, die Gesamtregisterdatei für jeden Kern ist etwas kleiner als 7 KB. Zum Vergleich: Die Nvidia GeForce RTX 2080 Ti- Registerdatei für das Streaming von Multiprozessoren (wie GPUs CPU-Kernanaloga nennen) ist 256 KB groß.

Register sind wie der Cache SRAMs, aber ihre Geschwindigkeit überschreitet nicht die Geschwindigkeit der ALUs, die sie bedienen. Sie übertragen Daten in einem Taktzyklus. Sie sind jedoch nicht zum Speichern großer Datenmengen (nur eines Elements) ausgelegt, sodass immer größere Speicherblöcke neben ihnen stehen: Dies ist der Cache der ersten Ebene (Ebene 1).

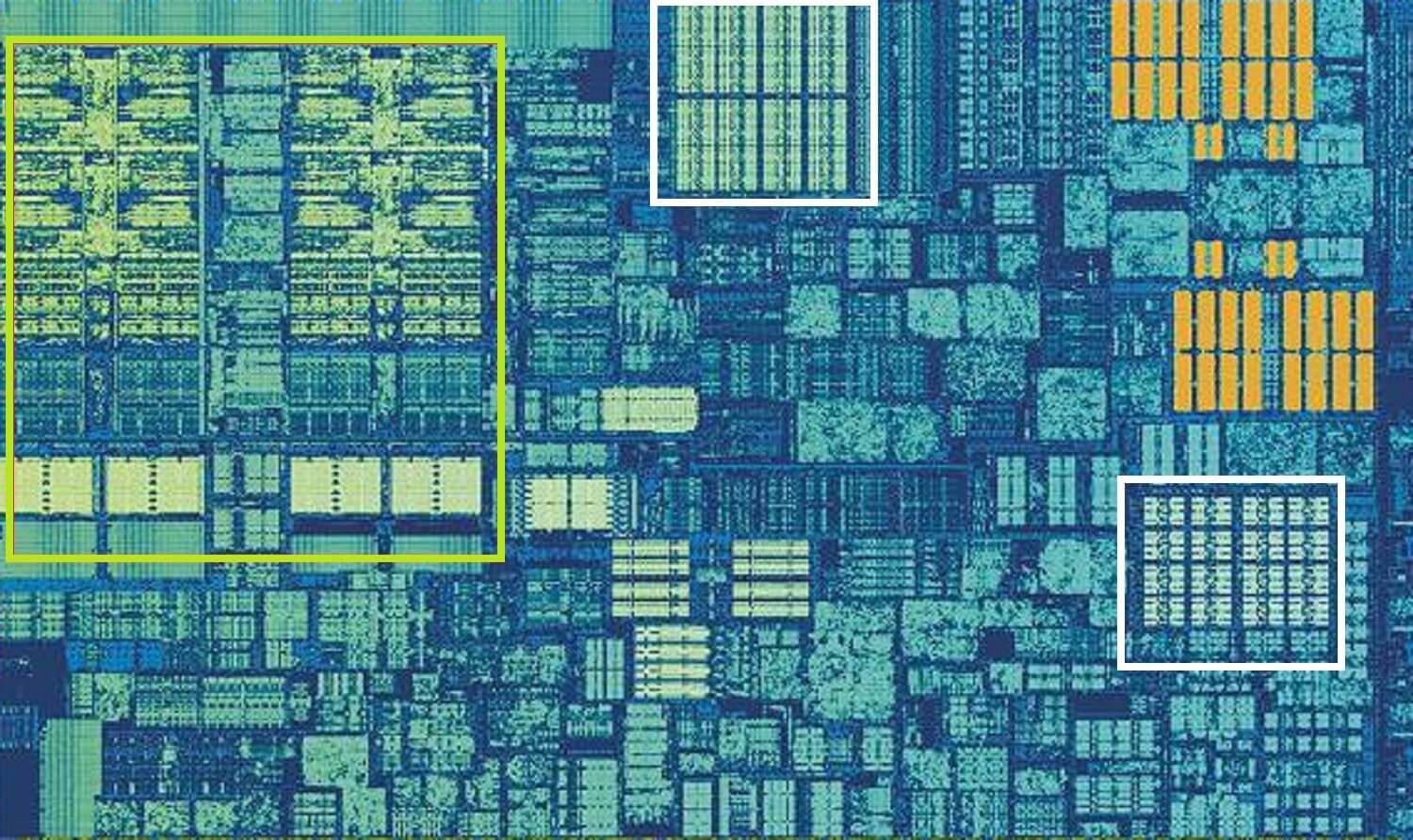

Ein Intel Skylake-Prozessorkern. Quelle: Wikichip

Das obige Bild ist eine vergrößerte Ansicht eines der Kerne des Intel Skylake- Desktop-Prozessors .

ALU- und Registerdateien befinden sich links und sind von einem grünen Rahmen umgeben. Oben auf dem Foto wird der Level 1-Datencache weiß angezeigt. Es enthält nicht viele Informationen, nur 32 KB, aber wie Register befindet es sich sehr nahe an logischen Blöcken und arbeitet mit ihnen mit der gleichen Geschwindigkeit.

Ein weiteres weißes Rechteck rechts zeigt den Befehls-Cache der Ebene 1 mit einer Größe von ebenfalls 32 KB. Wie der Name schon sagt, werden verschiedene Befehle gespeichert, die in kleinere Mikrooperationen aufgeteilt werden können.(normalerweise mit μops bezeichnet), die ALUs ausführen müssen. Es gibt auch einen Cache für sie, der als Level 0 klassifiziert werden kann, da er kleiner (enthält nur 1.500 Operationen) und näher als L1-Caches ist.

Sie fragen sich vielleicht, warum diese SRAMs so klein sind? Warum sind sie nicht Megabyte groß? Zusammen nehmen die Daten- und Befehls-Caches fast den gleichen Bereich auf dem Chip ein wie die Hauptlogikblöcke, so dass eine Vergrößerung zu einer Vergrößerung des gesamten Chipbereichs führt.

Der Hauptgrund für die Größe von mehreren Kilobyte ist jedoch, dass mit zunehmender Speicherkapazität die zum Suchen und Abrufen von Daten erforderliche Zeit zunimmt. Der L1-Cache muss sehr schnell sein, daher gibt es einen Kompromiss zwischen Größe und Geschwindigkeit - bestenfalls dauert es ungefähr 5 Taktzyklen, um Daten aus diesem Cache abzurufen (mehr für Gleitkommawerte).

L2-Cache von Skylake: 256 KB SRAM

Wenn dies jedoch der einzige Cache im Prozessor wäre, würde seine Leistung auf eine unerwartete Hürde stoßen . Aus diesem Grund ist eine weitere Speicherebene in die Kernel integriert: der Level 2-Cache. Dies ist ein verallgemeinerter Speicherblock, der Anweisungen und Daten enthält.

Es ist immer größer als Level 1: In AMD Zen 2- Prozessoren sind bis zu 512 KB erforderlich, um genügend Daten für Caches niedrigerer Level bereitzustellen. Die Größe erfordert jedoch Opfer - das Auffinden und Übertragen von Daten aus diesem Cache dauert im Vergleich zu Level 1 etwa doppelt so lange.

In den Tagen des ersten Intel Pentium war der Level 2-Cache ein separater Chip, der entweder auf einer separaten kleinen Karte (wie DIMM-RAM) installiert oder in die Hauptplatine integriert war. Allmählich bewegte es sich in das Gehäuse des Prozessors selbst und schließlich wurde es vollständig in den Chipkristall integriert; Dies geschah im Zeitalter von Prozessoren wie dem Pentium III und dem AMD K6-III.

Diesem Erfolg folgte bald eine weitere Cache-Ebene, die zur Unterstützung niedrigerer Ebenen benötigt wurde, und sie kam pünktlich zur Blütezeit der Multi-Core-Chips an.

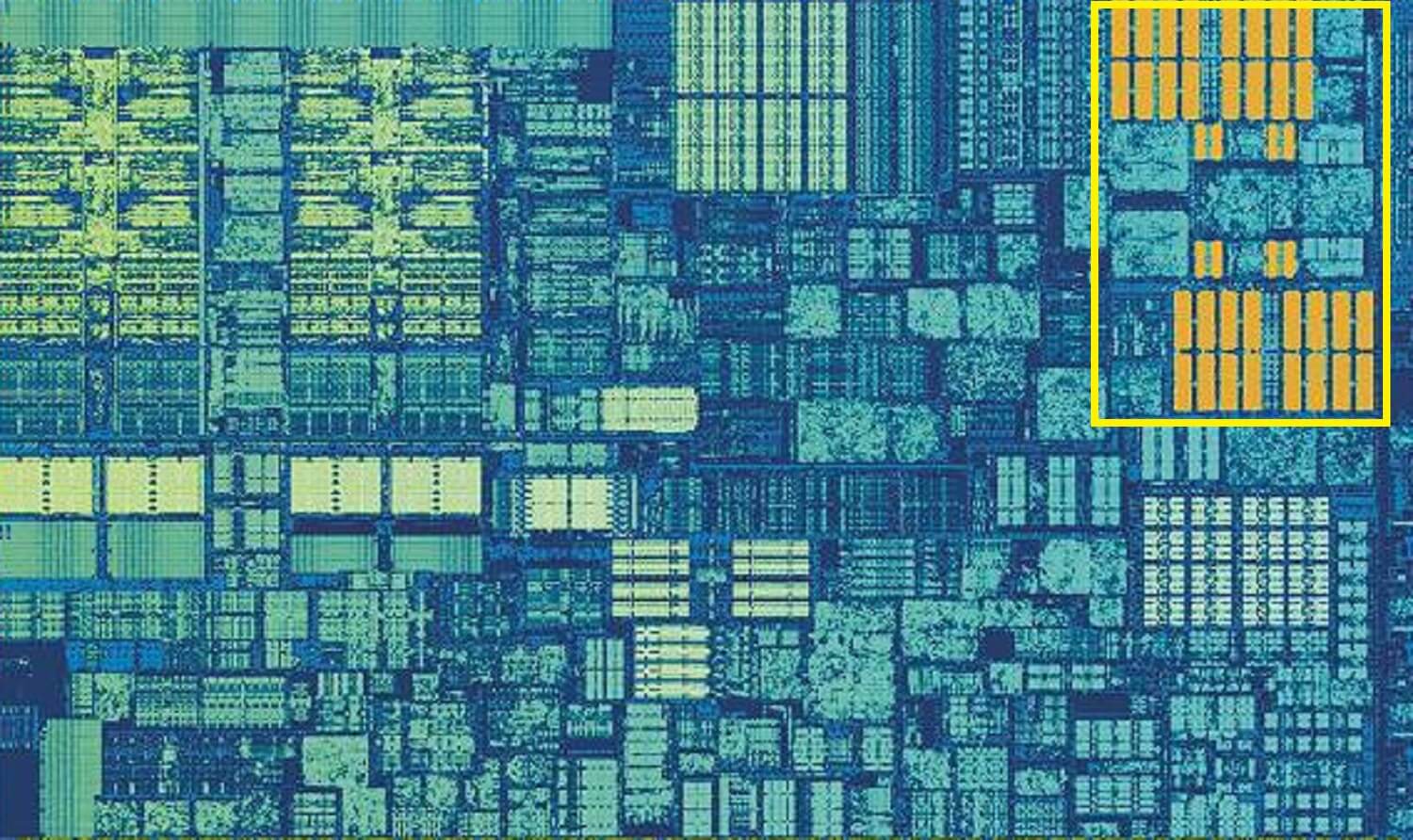

Intel Kaby Lake Chip. Quelle: Wikichip

Dieses Bild des Intel Kaby Lake- Chips zeigt links vier Kerne (die integrierte GPU nimmt fast die Hälfte des Chips ein und befindet sich rechts). Jeder Kern hat seinen eigenen "persönlichen" Satz von Caches der Stufen 1 und 2 (hervorgehoben in weißen und gelben Feldern), aber sie haben auch einen dritten Satz von SRAM-Blöcken.

Der Cache der dritten Ebene (Ebene 3) befindet sich zwar direkt neben einem Kern, ist jedoch allen anderen völlig gemeinsam. Jeder Kern kann frei auf den Inhalt des L3-Cache eines anderen Kerns zugreifen. Es ist viel größer (2 bis 32 MB), aber auch viel langsamer und liegt im Durchschnitt über 30 Zyklen, insbesondere wenn der Kernel Daten verwenden muss, die sich in einem weit entfernten Cache-Block befinden.

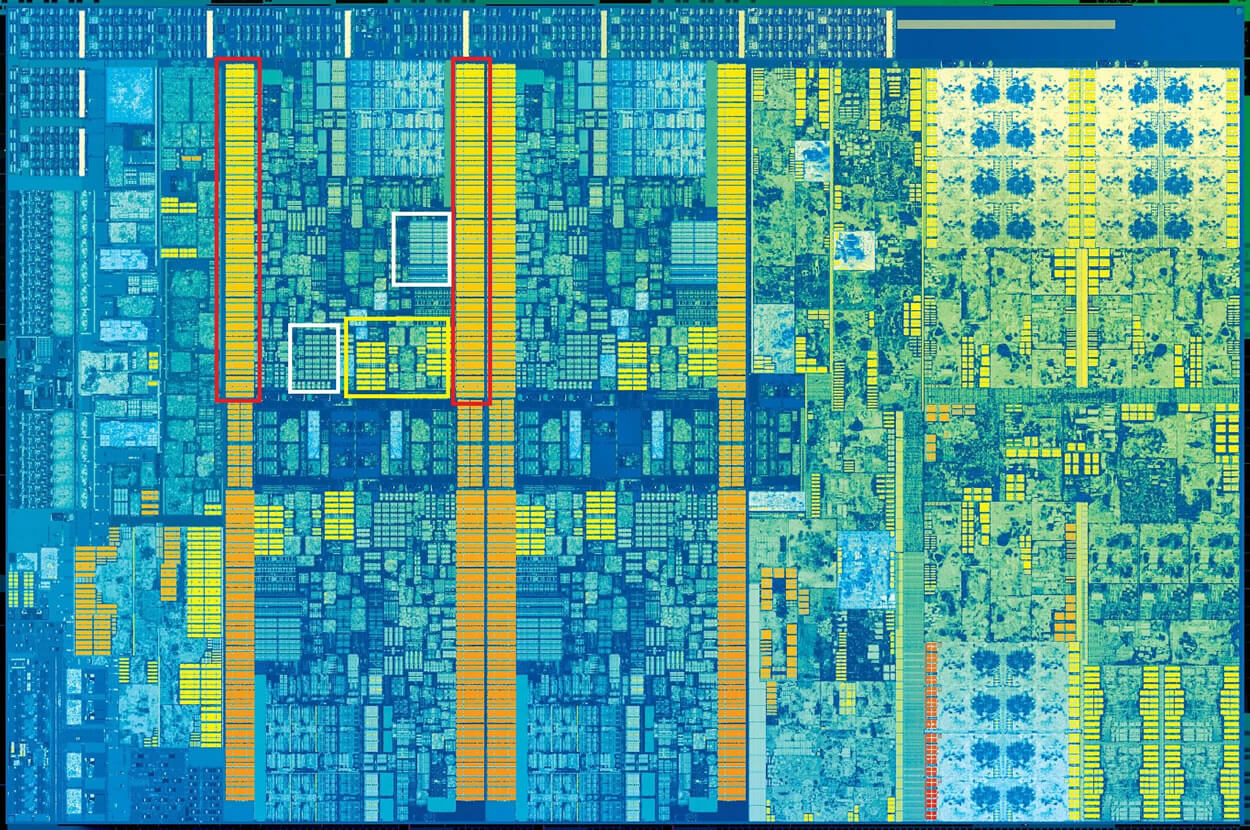

Im Folgenden wird ein Kern der AMD Zen 2-Architektur dargestellt: 32 KB Level 1-Daten- und Anweisungs-Caches (in weißen Feldern), 512 KB Level 2-Cache (in gelben Feldern) und ein riesiger 4 MB L3-Cache-Block (in roten Feldern).

Vergrößert einen einzelnen Kern eines AMD Zen 2-Prozessors. Quelle: Fritzchens Fritz

Aber warten Sie: Wie können 32 KB mehr physischen Speicherplatz beanspruchen als 512 KB? Wenn Level 1 so wenig Daten speichert, warum sind sie im Vergleich zu L2- und L3-Caches unverhältnismäßig groß?

Nicht nur Zahlen

Der Cache verbessert die Leistung, indem er die Übertragung von Daten in logische Blöcke beschleunigt und eine Kopie häufig verwendeter Anweisungen und Daten in der Nähe aufbewahrt. Die im Cache gespeicherten Informationen sind in zwei Teile unterteilt: die Daten selbst und den Ort, an dem sie sich ursprünglich im Systemspeicher befinden - diese Adresse wird als Cache-Tag bezeichnet .

Wenn der Prozessor eine Operation ausführt, die Daten aus / in den Speicher lesen oder schreiben muss, überprüft er zunächst die Tags im Level 1-Cache. Wenn die erforderlichen Daten vorhanden sind (ein Cache-Treffer ist aufgetreten ), sind diese Daten fast vollständig sofort. Ein Cache-Fehler tritt auf, wenn ein erforderliches Tag nicht auf der untersten Ebene im Cache gefunden wird.

Im L1-Cache wird ein neues Tag erstellt, und der Rest der Prozessorarchitektur übernimmt die Aufgabe. In anderen Ebenen des Caches (ggf. bis zum Hauptspeicher) werden die Daten für dieses Tag gesucht. Um jedoch Speicherplatz im L1-Cache für dieses neue Tag freizugeben, muss etwas in L2 geworfen werden.

Dies führt zu einem nahezu konstanten Mischen der Daten, das in nur wenigen Taktzyklen durchgeführt wird. Der einzige Weg, dies zu erreichen, besteht darin, eine komplexe Struktur um SRAM herum zu erstellen, um die Datenverwaltung zu übernehmen. Mit anderen Worten, wenn der Prozessorkern nur aus einer ALU bestehen würde, wäre der L1-Cache viel einfacher. Da es jedoch Dutzende von ihnen gibt (und viele von ihnen mit zwei Befehlsströmen jonglieren), benötigt der Cache viele Verbindungen, um Daten zu verschieben.

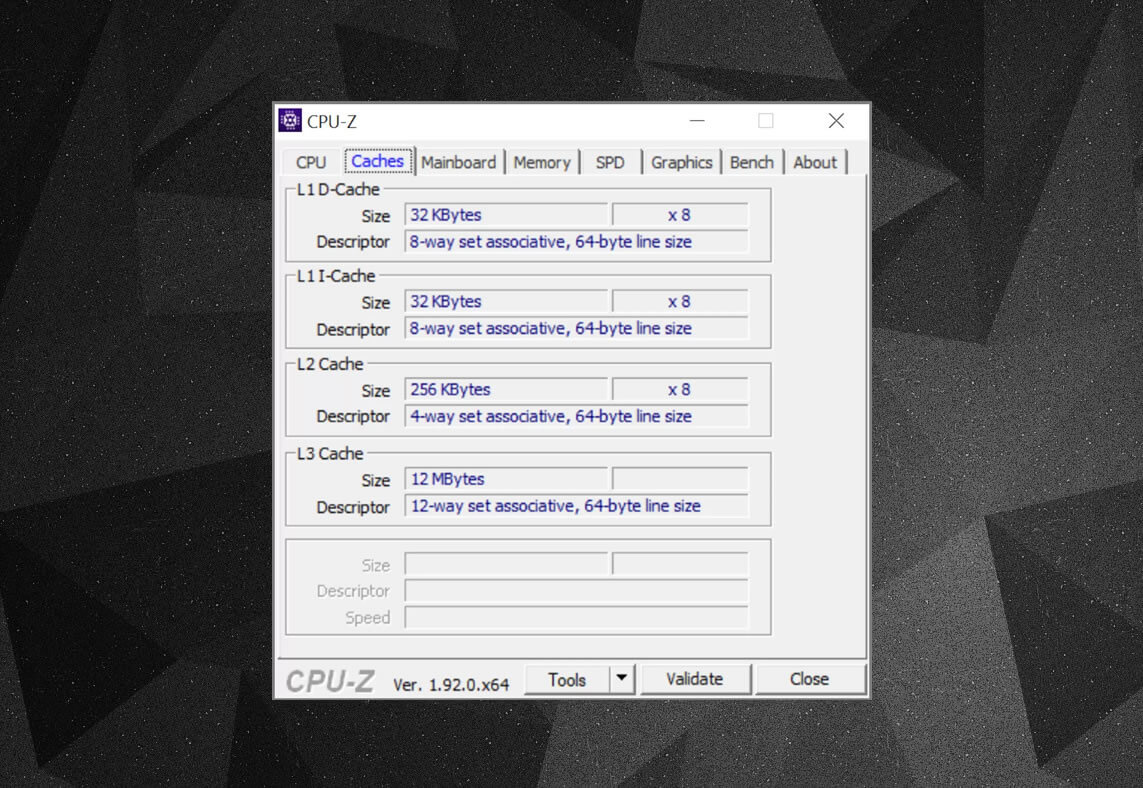

Sie können freie Software wie CPU-Z verwenden , um die Cache-Informationen im Prozessor Ihres Computers zu überprüfen . Aber was bedeuten all diese Informationen? Ein wichtiges Element ist die festgelegte assoziative Bezeichnung , die die Regeln angibt, nach denen Datenblöcke aus dem Systemspeicher in den Cache kopiert werden.

Die obigen Cache-Informationen gelten für Intel Core i7-9700K . Jeder seiner Level 1-Caches ist in 64 kleine Blöcke unterteilt, die als Sets bezeichnet werden , und jeder dieser Blöcke ist auch in Cache-Zeilen unterteilt.(64 Bytes groß). "Satzassoziativ" bedeutet, dass ein Datenblock aus dem System an Cache-Zeilen in einem bestimmten Satz gebunden ist und nicht frei an einen anderen Ort gebunden werden kann.

"8-Wege" bedeutet, dass ein Block 8 Cache-Zeilen im Satz zugeordnet werden kann. Je höher der Assoziativitätsgrad (dh je größer der „Weg“), desto höher ist die Wahrscheinlichkeit, dass ein Cache während einer Prozessorsuche getroffen wird, und desto geringer ist der Verlust, der durch Cache-Fehlschläge verursacht wird. Die Nachteile eines solchen Systems sind die erhöhte Komplexität und der erhöhte Stromverbrauch sowie die geringere Leistung, da für jeden Datenblock mehr Cache-Zeilen verarbeitet werden müssen.

Inklusive Cache L1 + L2, Opfer-Cache L3, Rückschreibrichtlinien, es gibt sogar ECC. Quelle: Fritzchens Fritz

Ein weiterer Aspekt der Cache-Komplexität hängt damit zusammen, wie Daten zwischen verschiedenen Ebenen gespeichert werden. Die Regeln sind in der Einschlussrichtlinie festgelegt . Beispielsweise verfügen Intel Core-Prozessoren über vollständig inklusive L1 + L3-Caches. Dies bedeutet, dass einige Daten in Ebene 1 beispielsweise in Ebene 3 vorhanden sein können. Dies scheint eine Verschwendung von wertvollem Cache-Speicherplatz zu sein. Der Vorteil besteht jedoch darin, dass der Prozessor das Tag in der unteren Ebene nicht benötigt, wenn er es nicht benötigt Durchsuchen Sie die oberste Ebene nach Daten.

In denselben Prozessoren ist der L2-Cache nicht inklusive: Alle dort gespeicherten Daten werden nicht auf eine andere Ebene kopiert. Dies spart Platz, führt jedoch dazu, dass das Speichersystem des Chips in L3 nach einem fehlenden Tag sucht (das immer viel größer ist). Opfer-Caches sind im Prinzip ähnlich, werden jedoch zum Speichern von Informationen verwendet, die von niedrigeren Ebenen übertragen werden. Beispielsweise verwenden AMD Zen 2-Prozessoren den Opfer-Cache L3, in dem einfach Daten von L2 gespeichert werden.

Es gibt andere Cache-Richtlinien, z. B. das Schreiben von Daten sowohl in den Cache als auch in den Hauptsystemspeicher. Diese werden als Schreibrichtlinien bezeichnet . Die meisten modernen Prozessoren verwenden Write-Back- Caches- Dies bedeutet, dass beim Schreiben von Daten in die Cache-Schicht eine Verzögerung auftritt, bevor eine Kopie davon in den Systemspeicher geschrieben wird. Meistens dauert diese Pause so lange, wie die Daten im Cache verbleiben - RAM empfängt diese Informationen nur, wenn sie aus dem Cache "gepoppt" werden.

Nvidia GA100-GPU mit 20 MB L1-Cache und 40 MB L2-Cache

Für Prozessorentwickler ist die Wahl der Cache- Größe, des Cache- Typs und der Richtlinie eine Frage des Ausgleichs zwischen der Notwendigkeit, die Prozessorleistung mit zunehmender Komplexität und Chip-Speicherplatz zu erhöhen. Wenn es möglich wäre, assoziative 1000-Kanal-20-MB-Level-1-Caches zu erstellen, damit diese nicht den Bereich von Manhattan belegen (und nicht die gleiche Menge an Strom verbrauchen), hätten wir alle Computer mit solchen Chips!

Die niedrigste Anzahl von Caches in modernen Prozessoren ist in den letzten zehn Jahren nahezu unverändert geblieben. Der Level 3-Cache wächst jedoch weiter an Größe. Wenn Sie vor zehn Jahren 999 US-Dollar für einen Intel i7-980X hatten, könnten Sie einen 12-MB-Cache haben. Heute für die Hälfte dieses Betragszum Kauf verfügbar 64 MB .

Zusammenfassend ist der Cache ein absolut unverzichtbares und fantastisches Gerät. Wir haben andere Arten von Caches in der CPU und der GPU nicht behandelt (z. B. assoziative Übersetzungspuffer oder Textur-Caches), aber da sie alle dieselbe einfache Struktur und Anordnung von Ebenen haben, wird es nicht schwierig sein, sie zu verstehen.

Hatten Sie einen Computer mit L2-Cache auf dem Motherboard? Wie wäre es mit geschlitzten Pentium II- und Celeron- Tochterplatinen (z. B. 300a )? Erinnerst du dich an deinen ersten gemeinsam genutzten L3-Prozessor?

Werbung

Unser Unternehmen bietet Mietserver mit Prozessoren von Intel und AMD an. Im letzteren Fall sind dies epische Server! VDS mit AMD EPYC , CPU- Kernfrequenz bis 3,4 GHz. Die maximale Konfiguration beträgt 128 CPU-Kerne, 512 GB RAM, 4000 GB NVMe.