Möchten Sie wissen, wie Sie einen Job beim Entwerfen von Raumschiffelektronik bekommen? Ich habe kürzlich ein Interviewangebot für die Position des FPGA-Designers für Blue Origin erhalten (siehe oben). Persönlich brauche ich eine solche Position nicht (ich habe bereits eine ASIC-Designerposition in einem anderen Unternehmen), aber ich habe festgestellt, dass die technischen Anforderungen für Bewerber in Blue Origin genau mit dem Inhalt des Seminars für Schüler und Jugendliche übereinstimmen , das vom 15. bis 17. September stattfinden wird auf der ChipEXPO in Skolkovo mit Unterstützung von RUSNANO. Natürlich werden wir auf dem Seminar Verilog- und FPGA-Technologien nur auf der ersten Ebene ansprechen: Grundkonzepte und einfache, aber bereits interessante Beispiele. Um danach einen Job bei Blue Origin zu bekommen, müssen Sie noch einige Jahre studieren und arbeiten.

Aufgrund des Coronavirus wird das Seminar abgelegen sein, sodass nicht nur Schüler und Studenten aus Moskau, sondern auch ganz Russland, die Ukraine, Kasachstan, Kalifornien und andere Länder und Regionen teilnehmen können. Dozenten und Ingenieure von MIET, HSE MIEM, MIPT, der Polytechnischen Universität Tschernihiw, der Universität Samara, IVA Technologies und fpga-systems.ru werden physisch Vorlesungen halten und die Teilnehmer aus der Ferne unterstützen .

Um zuerst noch vor dem Seminar teilnehmen zu können, müssen Sie drei Teile eines theoretischen Kurses von RUSNANO unter dem allgemeinen Titel "Wie die Entwickler intelligenter Nanochips arbeiten" absolvieren: "Vom Transistor zur Mikroschaltung", "Logische Seite der digitalen Schaltung", "Physikalische Seite der digitalen Schaltung". Dieser Kurs ist wichtig, damit Sie verstehen, was Sie während des Workshops tun. Nach Erhalt einer Bescheinigung über den Abschluss des theoretischen Online-Kurses können Sie zum RUSNANO-Büro in Moskau gehen und eine kostenlose Gebühr für ein praktisches Seminar erhalten (wenn sie bleiben, haben Schulkinder Vorrang). Mit diesem Board können Sie vor, während und nach dem Skolkovo-Seminar zu Hause arbeiten.

Wie man bezahlt wird, sich auf das Seminar vorbereitet und was darauf steht:

Anweisungen zum Erhalten einer Gebühr finden Sie auf der STEMford-Website . STEMford ist ein Bildungsprogramm für Schüler von eNano , einer Tochtergesellschaft der RUSNANO Foundation for Infrastructure Educational Programs. Hier ist ihr Büro zu besuchen:

Vor dem Labor muss Intel Quartus Prime Lite Edition auf Ihrem Computer installiert sein. Anweisungen dazu finden Sie im kostenlosen Fragment des Buches "Digitale Synthese: Ein praktischer Kurs", herausgegeben von A. Yu. Romanov, Yu. V. Panchul. DMK Press, 2020.

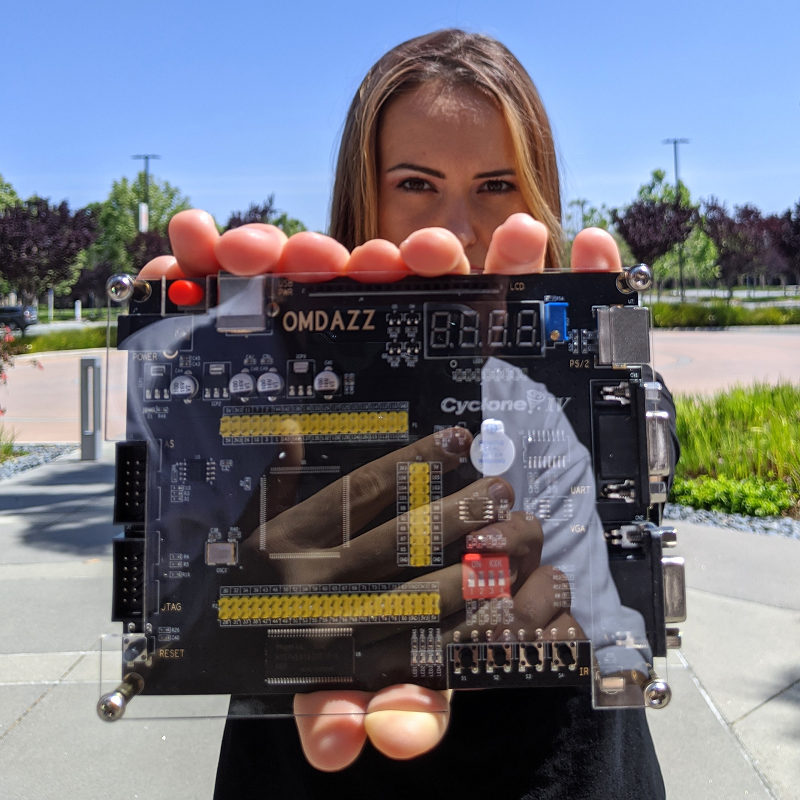

Im Allgemeinen ist "Digital Synthesis" ein nützliches Buch für ein Seminar. Es beschreibt Übungen, die auf dem Seminar mit einigen Variationen vorgestellt werden, obwohl sie beispielsweise anstelle des schoolMIPS-Bildungsprozessors moderner sindschoolRISCV : Am Ende des Buches Digital Synthesis gibt es ein ziemlich amüsantes Interview mit einigen Jungvermählten, Vladislav und Elena Sharshin, die Intel zusammen mit ihrem Kollegen Andrei Papushin nach Kalifornien gebracht hat, um den Silbersieg beim InnovateFPGA-Wettbewerb zu erringen: Hier ist eines der Boards, die für das Seminar verwendet werden. Wenn nicht genügend Boards für Sie vorhanden sind oder wenn Sie kein Student sind, können Sie ein Board bei AliExpress und an anderen Orten bestellen: 1 , 2 , 3 , 4 : Was wird während des Seminars passieren? Hier sind die Teile des Programms :

15 . .

: , « » ().

15.00. , .

15.15-15.30. -: Apple iPhone: .

, . , .

15.30-16.00. : Verilog. /FPGA Intel Quartus Prime Lite Edition. .

16.00-16.30.

///-, , c .

16.30-17.00. .

17.00-17.30. : , .

17.30-18.00. .

18.00-19.00. ZEOWAA OMDAZZ Intel FPGA Cyclone IV: : ( ). Terasic DE10-Lite Intel FPGA MAX10: : ( ).

19.00-21.00. , : , , ,

.

Der erste Tag basiert auf den Erfahrungen mit dem letztjährigen Seminar in Moskau, die in einem Artikel über Habré beschrieben werden : Der

zweite Tag basiert auf den Erfahrungen mit der Abhaltung einer Sommerschule in Zelenograd im letzten Jahr und Seminaren in Samara:

16 . .

: , , , .

15.00-15.15. -: : , .

.

15.15-15.30. : VGA.

.

15.30-16.00. .

16.00-16.30. . Digilent Basys3 Xilinx FPGA Artix-7. .

, fpga-systems.ru.

16.30-17.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

17.00-17.30. : Linear Feedback Shift Registers (LFSR) . Verilog VHDL LFSR . LFSR VGA .

, .

17.30-18.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

18.00-19.00. .

.

18.00-21.00. , . .

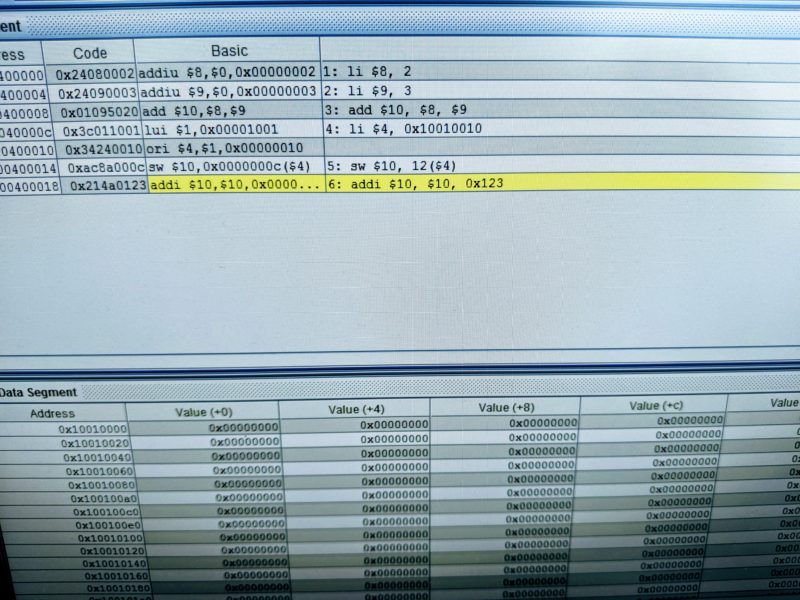

Der dritte Tag basiert auf den Erfahrungen des Bildungsprogramms mit Prozessoren von Stanislav Zhelnio und Alexander Romanov . Erst bevor sie den schoolMIPS-Lernprozessor entwickelt und verwendet haben, werden wir jetzt schoolRISCV verwenden. Die RISC-V-Architektur ist MIPS und anderen RISC-Architekturen (SPARC, ARM, POWER usw.) sehr ähnlich, wurde jedoch von ihren Krücken befreit, was auf einfachen Prozessoren sinnvoll war, aber komplexe störte (Registerfenster in SPARC, die in Software mit bedeutungslos sind) ein großer Stapel; Verzweigungsverzögerungsschlitze in MIPS bis Rev6, die in einer einfachen statischen Pipeline mit sequentiellem Abrufen von Anweisungen gut sind, in einer dynamischen Pipeline jedoch zu Kopfschmerzen führen usw.).

Da es in Russland mindestens drei Unternehmen gibt, die Prozessoren auf der RISC-V-Architektur entwerfen, ist dies ein guter Kandidat für einen zukünftigen russischen High-End-Embedded- und möglicherweise sogar Desktop- und Server-Prozessor, und da RISC-V MIPS als funktionierendes System sicher ersetzt Pferde für architektonische und mikroarchitektonische Experimente an Weltuniversitäten, es ist besser, Schulkinder darauf zu unterrichten.

17 . .

— , ..., . .. (), « » ( ).

15.00-15.15. -: ENIAC , IBM/360 Cray-1 Intel, ARM RISC-V: , .

.

15.15-16.30. : . RISC-V .

, - .

16.30-17.30. : . schoolRISCV, . .

, IVA Technologies.

17.30-17.30. . .

.

17.30-18.00 Uhr. Abschlussvorlesung: Die nächsten Schritte zur Beherrschung des Entwurfs digitaler Schaltungen und zur Anwendung dieses Wissens auf das Design eingebetteter Systeme und Beschleuniger für die Berechnung künstlicher Intelligenz.

Alexander Yurievich Romanov.

18.00-21.00 Uhr. Zusätzliche Übungen und individuelle Projekte für Schüler, um den Prozessor zu ändern und in Peripheriegeräte zu integrieren. Mit Hilfe von Studenten und Doktoranden der Mikroelektronik von teilnehmenden Universitäten.

Hier ist Stanislav Zhelnio, der im letzten Sommer in Zelenograd Schulkinder unterrichtet: Wir

sehen uns bei einem Seminar auf der virtuellen ChipEXPO in Skolkovo! Wir werden versuchen, einen Teil der Veranstaltung dort abzuhalten und mit Hilfe von Lehrern von MIET, HSE MIEM und MIPT zu leben, aber wenn das Virus dies nicht zulässt, werden wir es auf verteilte Weise durchführen.