Einführung

Zeitbeschränkungen sind einige Informationen, mit denen das Zeitanalyse-Dienstprogramm im CAD-System berechnen kann, ob die Daten alle Register des Projekts erfolgreich durchlaufen. Der Benutzer muss diese Einschränkungen selbst berechnen und in die Zeitbeschränkungsdatei eintragen. Ohne diese Einschränkungen schreibt der Benutzer ein Projekt nach dem Zufallsprinzip, ohne seine Leistung zu überprüfen, und der Compiler schwört, dass er keine Einschränkungen gefunden hat.

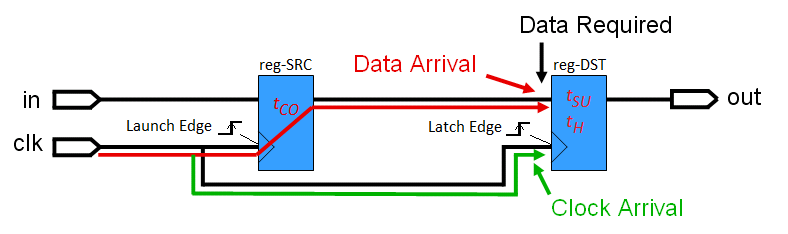

Im vorherigen Artikel ( Link) Ich habe darüber gesprochen, was die Datenübertragung zwischen zwei Registern ist und wie die Ausführung von Zeitbeziehungen bei der Datenübertragung innerhalb des FPGA berechnet wird, wenn beide Register in Betracht gezogen werden, liegen die Pfade von Taktsignalen und Datensignalen innerhalb des FPGA. Aus diesem Artikel muss ein Verständnis des Konzepts der synchronen Logik als Netzwerk abgeleitet werden, das aus einer Vielzahl von Übertragungen zwischen Registern (Abb. 1) und dem Begriff "Slack" (Abb. 2) besteht.

In diesem Artikel werden Fälle der Datenübertragung betrachtet, bei denen sich eines der beiden Übertragungsregister außerhalb des FPGA befindet - dies ist ein Register eines externen Geräts - eines Mikrocontrollers, eines ADC usw.

Zahl: 1. Das Schema der Datenübertragung zwischen Registern vom Quellregister (Quelle) zum Zielregister (Ziel).

Zahl: 2. Die Bedeutung von Durchhängen relativ zur Erfassungsfront am Eingang des Empfangsregisters.

Allgemeine Formeln zur Berechnung des Durchhangs, abgeleitet im vorherigen Artikel:

minSetupSlack=minDataRequired−maxDataArrival=

=S.R.+MindesttC.L.K.tÖD.S.T.- -maxtC.L.K.tÖS.R.C.- -maxtS.U.- -maxtC.Ö- -maxtD.

MindestH.ÖldS.leinck=MindestD.einteinEINrrichveinl- -maxD.einteinR.equichred=

=- -H.R.+MindesttC.L.K.tÖS.R.C.- -maxtC.L.K.tÖD.S.T.+MindesttC.Ö- -maxtH.+MindesttD.

Lassen Sie uns die Bedingungen durchgehen.

Durchhang ist eine Zeitspanne. Es muss positiv sein.

Voreingestellte Zeit (Rüstzeit,tS.U.) - die Mindestzeit, zu der sich die Daten bereits am Eingang des Empfangsregisters befinden müssen, wenn die Taktfront am Takteingang des Empfängers ankommt.

Haltezeit (Haltezeit,tH.) Ist die Mindestzeit, die die Daten noch am Eingang des Empfängers halten müssen, nachdem die Taktfront am Takteingang des Empfängers angekommen ist.

Antwortzeit registrieren (Zeit von der Uhr bis zur Ausgabe,tC.Ö) Ist die Zeit vom Eintreffen der Taktfront bis zum Takteingang des Quellregisters bis zum Auftreten neuer stabiler Daten an seinem Ausgang.

SR und HR sind Setup and Hold Relationship, die Differenz zwischen den Momenten der Vorderseite des Captures und der Vorderseite des Triggers an der Quelle der Uhr unter Berücksichtigung der Instabilität. Bei der Analyse interner FPGA-Übertragungen werden nur die ansteigenden Flanken des Takts berücksichtigt, so dass dieser Ausdruck vereinfacht wirdS.R.=T.- -C.S.U.,H.R.=C.H.U.... Da Schnittstellen jedoch häufig unterschiedliche Fronten verwenden, sollte eine allgemeinere Darstellung verwendet werden.

Der voreingestellte / gehaltene Taktjitter (CSU / CHU) ist ein Maß für den Taktjitter. In den Berechnungen trägt es die Bedeutung des "Nur für den Fall" -Randes, um die Phänomene zu berücksichtigen, die durch die unvollständige Häufigkeit des Gerinnsels verursacht werden.

tD. Ist die Zeit, die das Datensignal zwischen Registern wandert.

tC.L.K.tÖS.R.C.Ist die Zeit, die die Flanke des Taktsignals benötigt, um von der Taktquelle zum Takteingang des Quellenregisters zu gelangen. Und von der Taktquelle zum ZielregistertC.L.K.tÖD.S.T....

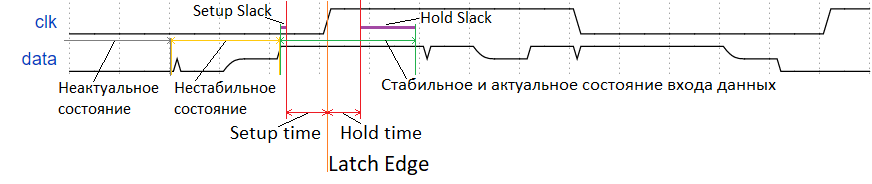

Die Signalpfade sind in Abbildung 3 dargestellt

. 3. Bezeichnung der Laufzeit der Pfade von Taktsignalen und Daten.

In diesem Bild sehen wir zwei Punkte - grün und rot. Beide sind Punkte, an denen die Pfade des Quell- und des Zielblocks noch nicht auseinander gegangen sind. Der grüne Punkt ist der Ausgang des globalen Taktpuffers, der Einstiegspunkt in das globale Taktnetz des FPGA, relativ zu dem die Takteingänge aller Register ungefähr gleich weit voneinander entfernt sind. Der rote Punkt ist ein beliebiger Punkt im globalen Uhrennetzwerk, an dem sich die Uhr wie am Eingang des Netzwerks noch nicht in zwei Kopien von sich selbst aufgeteilt hat, die in verschiedene Register gegangen sind. Aber nur der grüne Punkt ist ein geeigneter Punkt, um die Zeiten für den Durchgang von Uhren zu zählen, da er sich an einer Stelle befindet, die für den Compiler verständlich ist. In diesem Beispiel am Eingang des globalen Taktnetzwerks. Bei einfachen Schnittstellen, die von außen getaktet werden, kann der grüne Punkt jedoch nur ein FPGA-Zweig sein.Der Compiler kennt die Timings von diesem Punkt zu jedem der Register. Und der rote Punkt, der Ort des zufälligen Zusammentreffens der Pfade der beiden analysierten Uhren, ist für den Startpunkt nicht geeignet.

Arten der analysierten Übertragungen

Lassen Sie uns Fälle für die zeitliche Analyse klassifizieren. Die Analyse wird für jedes FPGA-Bein in Bezug auf einen bestimmten Block separat durchgeführt. Als Ergebnis der Analyse wird die Fähigkeit des Beins bewertet, Daten korrekt zu senden oder zu empfangen. Die externe Schnittstelle für den synchronen Datenaustausch zwischen dem FPGA und einem externen Gerät besteht aus mehreren Leitungen, die mit den Beinen verbunden sind. Von diesen ist eine Linie die Shred-Linie. Es muss zwischen den Registern auf beiden Seiten geteilt werden. Die verbleibenden Zeilen, eine oder mehrere, sind unidirektionale Eingabe- oder Ausgabezeilen. Was eine Eingangsleitung für ein FPGA ist, ist eine Ausgangsleitung für ein externes Gerät und umgekehrt. In diesem Artikel werden nur die einfachsten Fälle der zeitlichen Analyse betrachtet, sodass wir nicht auf asynchrone und selbstgesteuerte Schnittstellen sowie auf die Verwendung bidirektionaler E / A-Leitungen eingehen.

Analysefälle können nach der Richtung der Daten relativ zum FPGA (Input / Output) und der Richtung des Takts relativ zum FPGA klassifiziert werden (Daten werden vom FPGA / von einer externen Quelle getaktet). Für jeden Fall gibt es zwei Arten von Analysen (Setup / Hold). Insgesamt vier Fälle für die Analyse und acht Gleichungen, die wir ableiten müssen.

Ausgabe von Daten, die von einem internen FPGA-Takt getaktet werden

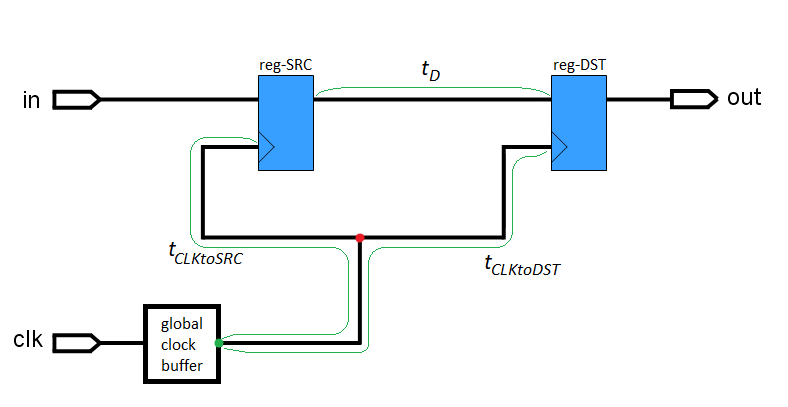

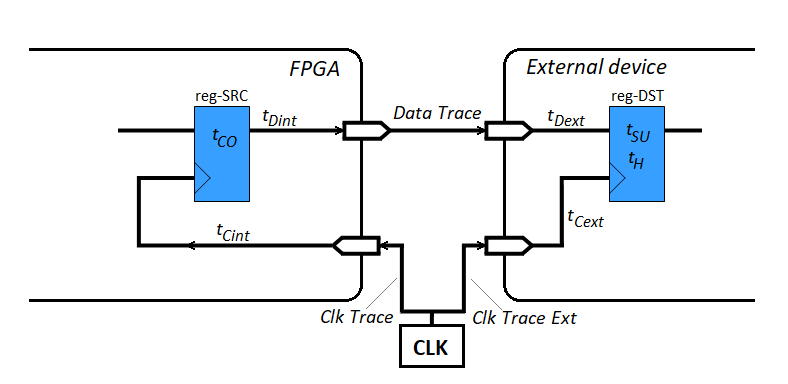

Betrachten Sie den Fall, in dem wir etwas auf unserem Fetzen herausgeben müssen (Abb. 4).

Das grundlegende Datenübertragungsschema hat sich nicht geändert. Aber die Register gehören jetzt zu zwei verschiedenen Mikroschaltungen, und der Datenpfad zwischen ihnen ist keine kombinatorische Logik, sondern nur Spuren auf der Platine. Und unsere Aufgabe ist es, die bekannten Slack-Formeln an eine etwas andere Situation anzupassen.

Zahl: 4. Übertragen Sie Daten auf Ihrer eigenen FPGA-Uhr nach außen.

In Abbildung 4 sehen wir ein Übertragungsschema zwischen den Registern. Es zeigt die Zeiten der Prozesse, die jedem der Register zugeordnet sind, und die Zeiten, für die Signale die Pfade durchlaufen.

Ich habe die folgende Indizierung festgelegt: Die Zeit, die sich auf die Daten bezieht, ist mit dem Buchstaben D gekennzeichnet. Die Zeit, die sich auf die Uhr bezieht, ist mit dem Buchstaben C gekennzeichnet. Wenn ein Ereignis innerhalb des FPGA auftritt, wird seine Zeit mit einem "int" -Index markiert, und wenn in einem externen Gerät, dann mit "ext". ... Die Zeit, die der Chunk benötigt, um von der Chunk-Quelle zum Chunk-Ausgangsstamm zu gelangen, hat den längsten Index "Cintout". DataTrace und ClkTrace sind die Laufzeiten der entsprechenden Leiterbahnen auf der Leiterplatte. Der "CLK" -Block symbolisiert eine Art interne Uhrquelle.

Das Hauptmerkmal der in der Abbildung genannten Mengen ist, dass sie alle positiv sind. Alle von ihnen sind gleich der absoluten Dauer aller physikalischen Prozesse, was bedeutet, dass sie physikalisch nur positive Werte sein können. Dies ist wichtig für weitere Überlegungen.

Jetzt werden wir uns die Analyse des voreingestellten Durchhangs genauer ansehen. In Abbildung 4 können wir die beobachteten Werte leicht mit den Begriffen der Slack-Formeln korrelieren:

Lassen Sie uns nun diese Gleichungen in die voreingestellte Slack-Formel einsetzen:tC.L.K.tÖS.R.C.=tC.ichnt

tD.=tD.ichnt+D.einteinT.reince+tD.ext

tC.L.K.tÖD.S.T.=tC.ichntÖut+C.lkT.reince+tC.ext

MindestS.etupS.leinck=MindestD.einteinR.equichred- -maxD.einteinEINrrichveinl=

=S.R.+MindesttC.L.K.tÖD.S.T.- -maxtC.L.K.tÖS.R.C.- -maxtS.U.- -maxtC.Ö- -maxtD.=

=S.R.+Mindest(tC.ichntÖut+C.lkT.reince+tC.ext)- -max(tC.ichnt)- -tS.U.- -tC.Ö- -

- -max(tD.ichnt+D.einteinT.reince+tD.ext)

Jetzt nutzen wir das Wissen, dass alle Begriffe in Klammern größer als Null sind. Wir wissen also, wie man solche Klammern öffnet: Das Minimum der Summe ist gleich der Summe der Minima, und das Maximum der Summe ist gleich der Summe der Maxima:

MindestS.etupS.leinck=S.R.+MindesttC.ichntÖut+MindestC.lkT.reince+MindesttC.ext- -maxtC.ichnt- -

- -tS.U.- -tC.Ö- -maxtD.ichnt- -maxD.einteinT.reince- -maxtD.ext

Lassen Sie uns nun die Begriffe an bestimmten Stellen neu anordnen, um die Begriffe der Prozesse innerhalb des FPGA und der Prozesse innerhalb des externen Geräts in Klammern zu gruppieren:

MindestS.etupS.leinck=S.R.- -(maxtC.ichnt+tC.Ö+maxtD.ichnt- -MindesttC.ichntÖut)+

+MindestC.lkT.reince- -maxD.einteinT.reince- -(maxtD.ext+tS.U.- -MindesttC.ext)

Was sehen wir in Klammern? Wenn Sie genau hinschauen und sich noch einmal daran erinnern, dass alle angegebenen Werte größer als Null sind, können wir sagen, dass wir einen Ausdruck einer bestimmten äquivalenten (mit einem Sternchen) Antwortzeit des FPGA-Registers und der äquivalenten Voreinstellungszeit des externen Geräteregisters sehen:

maxtC.ichnt+tC.Ö+maxtD.ichnt- -MindesttC.ichntÖut=maxt∗C.Ö

maxtD.ext+tS.U.- -MindesttC.ext=maxt∗S.U.

MindestS.etupS.leinck=S.R.- -maxt∗C.Ö+MindestC.lkT.reince- -maxD.einteinT.reince- -maxt∗S.U.

Warum verwenden wir keine äquivalenten Werte, wenn die Chiphersteller sie bereits unter Berücksichtigung ihrer internen Verzögerungen für uns berechnet haben? Äquivalente Werte auf der FPGA-Seite werden vom Compiler ohne Benutzereingriff berechnet, und die äquivalenten Werte des externen Geräts werden im Datenblatt des Geräts explizit angegeben.

Schauen wir uns nun den letzten Ausdruck genauer an. Darin sind dem Analysator die ersten drei Terme bereits bekannt, da wir ihm bereits die Betriebsfrequenz und die Größe der Instabilität angegeben haben. Der Compiler hat nachverfolgt und der Analysator kennt die äquivalente Antwortzeit seines Registers. Dies bedeutet, dass der Analysator die Dauer aller Prozesse im FPGA kennt. Die letzten drei Begriffe sind jedoch für jedes Bein eindeutig, und der Benutzer muss sie selbst berechnen und dem Analysator als Zahl angeben. Was ist das für eine Nummer? Wenn wir uns die letzten drei Begriffe genauer ansehen, werden wir sehen, dass sie als negatives Maximum eines bestimmten Wertes interpretiert werden können:

MindestC.lkT.reince- -maxD.einteinT.reince- -maxt∗S.U.=- -maxÖutputD.eleiny

Und dieser Wert entspricht sinnvollerweise der Verzögerung von allem, was außerhalb des FPGA geschieht, relativ zu allem, was innerhalb des FPGA geschieht. Es heißt so - die Ausgangsverzögerung, Ausgangsverzögerung.

Fassen wir zusammen:

MindestS.etupS.leinck=S.R.- -maxt∗C.Ö- -maxÖutputD.eleiny

maxÖutputD.eleiny=maxD.einteinT.reince+maxt∗S.U.- -MindestC.lkT.reince=

=max(D.einteinT.reince+t∗S.U.- -C.lkT.reince)

Nun werden wir eine ähnliche Gleichung für den Retentionsspiel ableiten. Erinnern Sie sich an die allgemeine Gleichung und ersetzen Sie sie durch neue Begriffe:

Öffnen wir die Klammern und gruppieren die Begriffe sofort um jedes der Register:MindestH.ÖldS.leinck=MindestD.einteinEINrrichveinl- -maxD.einteinR.equichred=

=- -H.R.+MindesttC.L.K.tÖS.R.C.- -maxtC.L.K.tÖD.S.T.+MindesttC.Ö- -maxtH.+MindesttD.=

=- -H.R.+Mindest(tC.ichnt)- -max(tC.ichntÖut+C.lkT.reince+tC.ext)+tC.Ö- -tH.+

+Mindest(tD.ichnt+D.einteinT.reince+tD.ext)

Und wieder sehen wir, wie die Begriffe dieses Mal in äquivalente Mengen gruppiert werden tC.Ö und tH.::MindestH.ÖldS.leinck=- -H.R.+(tC.Ö+MindesttC.ichnt+MindesttD.ichnt- -maxtC.ichntÖut)- -

- -maxC.lkT.reince+MindestD.einteinT.reince- -(tH.- -MindesttD.ext+maxtC.ext)

Und die letzten drei Begriffe können als minimale externe Verzögerung verstanden werden:MindestH.ÖldS.leinck=- -H.R.+Mindestt∗C.Ö+MindestD.einteinT.reince- -maxC.lkT.reince- -maxt∗H.

MindestD.einteinT.reince- -maxC.lkT.reince- -maxt∗H.=MindestÖutputD.eleiny

Fassen wir zusammen:

MindestH.ÖldS.leinck=- -H.R.+Mindestt∗C.Ö+MindestÖutputD.eleiny

MindestÖutputD.eleiny=Mindest(D.einteinT.reince- -C.lkT.reince- -t∗H.)

Es sollte betont werden, dass MindestÖutputD.eleiny und maxÖutputD.eleiny- Dies ist das Minimum und Maximum, nicht absolut der gleiche Wert. Jede voreingestellte Analyse und Aufbewahrungsanalyse berücksichtigt unterschiedliche Situationen und unterschiedliche externe Verzögerungen. Dies bedeutet, dass die Begriffe, wie aus den Formeln ersichtlich, unterschiedlich verstanden werden.

Ausgabe von Daten, die von einer externen Uhr getaktet werden

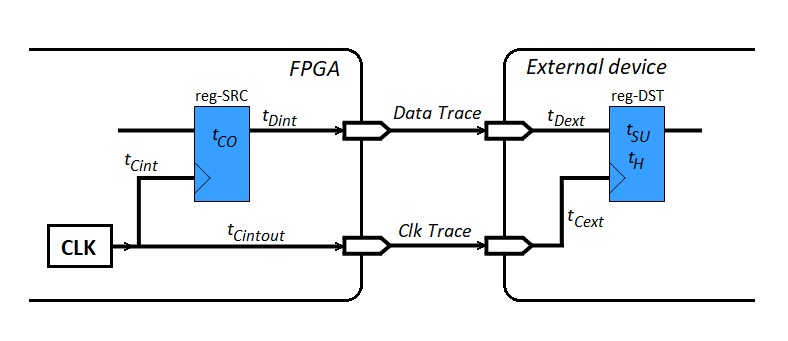

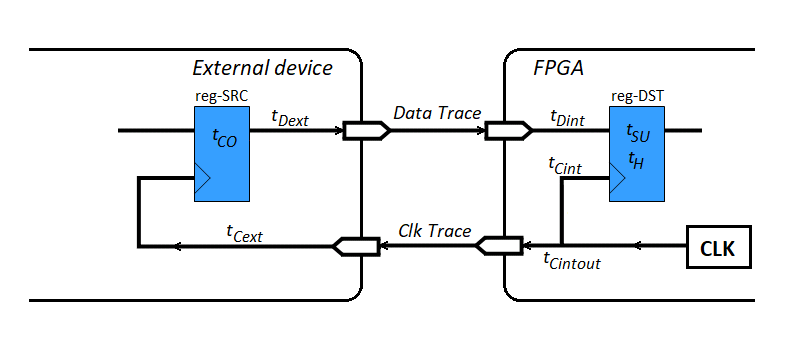

Kommen wir nun zu dem Fall, in dem wir etwas nach außen geben müssen, aber nach einer Uhr außerhalb des FPGA (Abb. 5). Im Allgemeinen befindet sich die Taktquelle außerhalb des FPGA, insbesondere kann sie sich innerhalb eines externen Geräts befinden.

Zahl: 5. Datenübertragung über eine externe Uhr nach außen.

In Abbildung 5 sehen wir die Quelle des Shreds draußen. Dementsprechend ist die MengetC.ichntÖutund die Zeit für den Übergang des Blocks zum externen Gerät "Clk Trace Ext" erschien.

In Abbildung 5 korrelieren wir die beobachteten Werte mit den Begriffen der allgemeinen Slack-Formeln:

tC.L.K.tÖS.R.C.=C.lkT.reince+tC.ichnt

tD.=tD.ichnt+D.einteinT.reince+tD.ext

tC.L.K.tÖD.S.T.=C.lkT.reinceE.xt+tC.ext

Mit diesen Ausdrücken öffnen wir die Begriffe in der voreingestellten Slack-Formel, gruppieren sie sofort nach Registern und erhalten die entsprechende Form:

MindestS.etupS.leinck=MindestD.einteinR.equichred- -maxD.einteinEINrrichveinl=

=S.R.+MindesttC.L.K.tÖD.S.T.- -maxtC.L.K.tÖS.R.C.- -maxtS.U.- -maxtC.Ö- -maxtD.=

=S.R.- -(maxtC.ichnt+tC.Ö+maxtD.ichnt)- -maxD.einteinT.reince- -

- -(maxtD.ext+tS.U.- -MindesttC.ext)- -maxC.lkT.reince+MindestC.lkT.reinceE.xt=

=S.R.- -maxt∗C.Ö- -max(t∗S.U.+D.einteinT.reince+C.lkT.reince- -C.lkT.reinceE.xt)

MindestS.etupS.leinck=S.R.- -maxt∗C.Ö- -maxÖutputD.eleiny

maxÖutputD.eleiny=max(t∗S.U.+D.einteinT.reince+C.lkT.reince- -C.lkT.reinceE.xt)

Wir analysieren den Laderaum auf die gleiche Weise:

MindestH.ÖldS.leinck=MindestD.einteinEINrrichveinl- -maxD.einteinR.equichred=

=- -H.R.+MindesttC.L.K.tÖS.R.C.- -maxtC.L.K.tÖD.S.T.+MindesttC.Ö- -maxtH.+MindesttD.=

=- -H.R.+(MindesttC.ichnt+tC.Ö+MindesttD.ichnt)+MindestD.einteinT.reince+MindestC.lkT.reince- -

- -(tH.- -MindesttD.ext+maxtC.ext)- -maxC.lkT.reinceE.xt=

=- -H.R.+Mindestt∗C.Ö+MindestD.einteinT.reince+MindestC.lkT.reince- -maxC.lkT.reinceE.xt- -maxt∗H.

MindestH.ÖldS.leinck=- -H.R.+Mindestt∗C.Ö+MindestÖutputD.eleiny

MindestÖutputD.eleiny=Mindest(D.einteinT.reince+C.lkT.reince- -C.lkT.reinceE.xt- -t∗H.)

Wenn wir in diesem Schema einen bestimmten (aber häufigen) Fall betrachten, in dem sich die Quelle des Tricks in einem externen Gerät befindet, ändern sich die abgeleiteten Formeln nur dadurch, dass ClkTraceExt in ihnen gleich Null wird. Wenn Sie die Quelle der Uhr in das Innere des externen Geräts verschieben, wird das Gerinnsel innerhalb des externen Geräts in unseren Berechnungen mikroskopisch zwischen dem Taktausgang und dem Register verteilt. Dies wird jedoch vom Hersteller des externen Geräts berücksichtigt und in die entsprechenden Werte einbezogent∗S.U. und t∗H....

Eingabe von Daten, die von einem internen FPGA-Takt getaktet werden

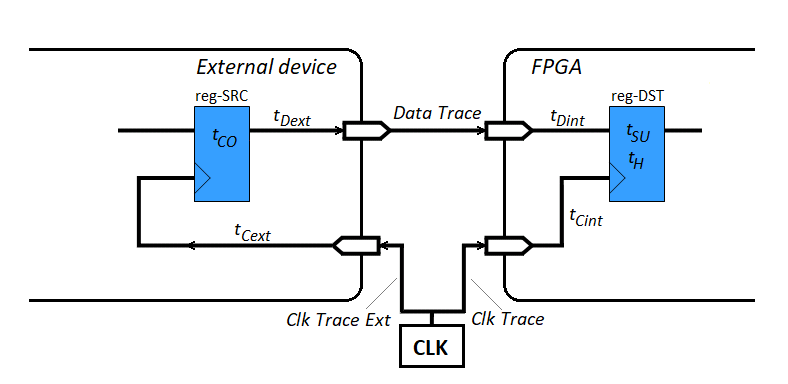

Wir wenden uns nun der Betrachtung der Eingangszweige der synchronen Schnittstelle zu. Das FPGA und das externe Gerät in Abbildung 6 werden ausgetauscht.

Zahl: 6. Empfangen von Daten auf Ihrer eigenen FPGA-Uhr.

Die Analyse eines solchen Schemas ist nicht komplizierter als die vorherigen.

Wir enthüllen, wir gruppieren ...tC.L.K.tÖS.R.C.=tC.ichntÖut+C.lkT.reince+tC.ext

tD.=tD.ext+D.einteinT.reince+tD.ichnt

tC.L.K.tÖD.S.T.=tC.ichnt

Und wir erhalten den Wert der externen Verzögerung, die wir dieses Mal als Eingabe bezeichnen werden:MindestS.etupS.leinck=MindestD.einteinR.equichred- -maxD.einteinEINrrichveinl=

=S.R.+MindesttC.L.K.tÖD.S.T.- -maxtC.L.K.tÖS.R.C.- -maxtS.U.- -maxtC.Ö- -maxtD.=

=S.R.- -(tS.U.+maxtD.ichnt- -MindesttC.ichnt+maxtC.ichntÖut)- -maxD.einteinT.reince- -

- -(tC.Ö+maxtD.ext+maxtC.ext)- -maxC.lkT.reince

MindestS.etupS.leinck=S.R.- -maxt∗S.U.- -maxichnputD.eleiny

maxichnputD.eleiny=max(D.einteinT.reince+t∗C.Ö+C.lkT.reince)

Jetzt lässt der Halt nach:

MindestH.ÖldS.leinck=MindestD.einteinEINrrichveinl- -maxD.einteinR.equichred=

=- -H.R.+MindesttC.L.K.tÖS.R.C.- -maxtC.L.K.tÖD.S.T.+MindesttC.Ö- -maxtH.+MindesttD.=

=- -H.R.- -(tH.- -MindesttD.ichnt+maxtC.ichnt- -MindesttC.ichntÖut)+MindestD.einteinT.reince+

+(tC.Ö+MindesttD.ext+MindesttC.ext)+MindestC.lkT.reince

MindestH.ÖldS.leinck=H.R.- -maxt∗H.+MindestichnputD.eleiny

MindestichnputD.eleiny=Mindest(t∗C.Ö+D.einteinT.reince+C.lkT.reince)

Eingabe von Daten, die von einer externen Uhr getaktet werden

Entsprechend dem gerändelten betrachten wir auch das Datenübertragungsschema und enthüllen die Begriffe der allgemeinen Formel.

Zahl: 7. Empfang von Daten auf externen Uhren.

tC.L.K.tÖS.R.C.=C.lkT.reinceE.xt+tC.ext

tD.=tD.ext+D.einteinT.reince+tD.ichnt

tC.L.K.tÖD.S.T.=C.lkT.reince+tC.ichnt

Voreingestellte Slack-Formel:

MindestS.etupS.leinck=MindestD.einteinR.equichred- -maxD.einteinEINrrichveinl=

=S.R.+MindesttC.L.K.tÖD.S.T.- -maxtC.L.K.tÖS.R.C.- -maxtS.U.- -maxtC.Ö- -maxtD.=

=S.R.- -(tS.U.+maxtD.ichnt- -MindesttC.ichnt)- -maxD.einteinT.reince- -

- -(tC.Ö+maxtD.ext+maxtC.ext)- -maxC.lkT.reinceE.xt+MindestC.lkT.reince=

=S.R.- -maxt∗S.U.- -max(t∗C.Ö+D.einteinT.reince+C.lkT.reinceE.xt- -C.lkT.reince)

MindestS.etupS.leinck=S.R.- -maxt∗S.U.- -maxichnputD.eleiny

maxichnputD.eleiny=max(t∗C.Ö+D.einteinT.reince+C.lkT.reinceE.xt- -C.lkT.reince)

Schlaffretentionsformel:

MindestH.ÖldS.leinck=MindestD.einteinEINrrichveinl- -maxD.einteinR.equichred=

=- -H.R.+MindesttC.L.K.tÖS.R.C.- -maxtC.L.K.tÖD.S.T.+MindesttC.Ö- -maxtH.+MindesttD.=

=- -H.R.- -(tH.- -MindesttD.ichnt+maxtC.ichnt)+MindestD.einteinT.reince+

+(tC.Ö+MindesttD.ext+MindesttC.ext)+MindestC.lkT.reinceE.xt- -maxC.lkT.reince

MindestH.ÖldS.leinck=- -H.R.- -maxt∗H.+MindestichnputD.eleiny

MindestichnputD.eleiny=Mindest(t∗C.Ö+D.einteinT.reince+C.lkT.reinceE.xt- -C.lkT.reince)

Befindet sich die Quelle der Uhr in einem externen Gerät, setzen Sie ClkTraceExt einfach mit Null gleich.

Visuelle Interpretation

Formeln sind sicherlich gut, aber wenn Sie zum ersten Mal in dieses Thema eintauchen, sehen die Formeln unverständlich und leblos aus. Ich möchte etwas klareres, damit die Formeln sichtbare Bedeutung bekommen. Okay, lassen Sie uns die physikalische Bedeutung der Formeln analysieren, zum Beispiel den Fall der Ausgabe von Daten durch eine externe Uhr . Ich möchte Sie daran erinnern, wie das Diagramm und die Formeln aussehen:

Abb. 8. Datenübertragung nach außen über eine externe Uhr.

MindestS.etupS.leinck=MindestD.einteinR.equichred- -maxD.einteinEINrrichveinl=

=S.R.- -maxt∗C.Ö- -maxt∗S.U.- -maxD.einteinT.reince- -maxC.lkT.reince+MindestC.lkT.reinceE.xt

MindestH.ÖldS.leinck=MindestD.einteinEINrrichveinl- -maxD.einteinR.equichred=

=- -H.R.+Mindestt∗C.Ö+MindestD.einteinT.reince+MindestC.lkT.reince- -maxC.lkT.reinceE.xt- -maxt∗H.

Während der Datenübertragung treten zwei Ereignisse auf: Das Quellregister wird ausgelöst und das Zielregister wird ausgelöst. Ereignisse treten auf, weil sie durch die aus der Cloc-Quelle austretenden Clok-Fronten ausgelöst werden. Von hier aus werden wir anfangen zu suchen.

Die Quelle der Uhr erzeugt eine Startfront und gelangt während ClkTrace zum FPGA. Dann wird das FPGA-Register während ausgelöstt∗C.Ö... Ferner werden die durch diese Operation erzeugten neuen Daten während der DataTrace vom FPGA zum externen Gerät übertragen.

Andererseits erzeugt die Quelle der Uhr auch eine Erfassungsfront, die während des ClkTraceExt zum externen Gerät gelangt.

Diese beiden Ereignisse treten am Dateneingang eines externen Geräts auf. Und hier ist es wichtig, dass die Daten dort ankommen, bevor das Empfangsregister mit der Erfassung beginnt. Sie sollten mindestens noch etwas Zeit haben.t∗S.U., oder noch besser. Der schlimmste Fall wird berücksichtigt, um sicherzustellen, dass dies wahr ist. Wenn es auch im schlimmsten Fall eine Reserve gibt, ist definitiv alles in Ordnung. Daher ist der schlechteste Moment der Datenankunft der späteste Moment.max(C.lkT.reince+t∗C.Ö+D.einteinT.reince)... Und der schlimmste Moment des Wartens auf Daten ist der früheste Moment,MindestC.lkT.reinceE.xt- -maxt∗S.U.... Und selbst im schlimmsten Fall sollte der zweite Moment später sein als der erste:

Hoffentlich gibt diese Erklärung mehr Aufschluss darüber, was los ist.L.eintchE.dGe+MindestC.lkT.reinceE.xt- -maxt∗S.U.>

>L.einunchE.dGe+max(C.lkT.reince+t∗C.Ö+D.einteinT.reince)

In diesem Ausdruck sehen wir die Momente der Fronten - LaunchEdge und LatchEdge, die normalerweise in den Begriffen SR und HR verborgen sind. Erinnern wir uns, was es ist. Bei der Preset- und Hold-Analyse werden vier Kanten berücksichtigt: Die

Setup-Startkante ist die Kante, die bewirkt, dass die Quelle die Daten sendet, die der Empfänger abfangen soll.

Hold Launch Edge ist die Vorderseite, die die Quelle zwingt, die nächsten Daten zu senden, wodurch verhindert werden kann, dass der Empfänger die vorherigen Daten abruft. Per Definition gibt es zwischen Setup LaunchEdge und Hold Launch Edge immer eine Taktperiode.

Die Setup Latch Edge ist die Vorderseite, die den Empfänger zwingt, Eingabedaten zu erfassen.

Hold Latch Edge ist dieselbe Setup Latch Edge. Das heißt, Latch Edge ist physisch eins, es werden einfach zwei Namen für Schönheit in zwei Arten von Analysen gegeben.

Innerhalb von FPGAs funktioniert die synchrone Logik normalerweise nur bei steigenden Flanken (Abbildung 9). In diesem Fall sind aus Sicht der Slack-Analyse die Voreinstellungen Setup Launch Edge und Setup Latch Edge um eine Taktperiode voneinander beabstandet, und aus Sicht der Analyse des Haltens stimmen Hold Launch Edge und Hold Latch Edge überein.

Zahl: 9. Gegenseitige Anordnung der Flanken in dem Fall, in dem beide Register durch die ansteigenden Flanken getaktet werden.

Es verbietet jedoch niemand, ein invertiertes Taktsignal an den Takteingang eines der beiden Register zu legen und es dadurch an der fallenden Flanke des Takts arbeiten zu lassen. Dies geschieht übrigens häufig in denselben SPI-Schnittstellen. Schauen wir uns diese Option genauer an.

Betrachten wir die Situation der Daten, die vom FPGA durch einen externen Takt ausgegeben werden, aber eines der beiden Register arbeitet mit einem invertierten Takt, dh entlang einer fallenden Flanke. Sei es ein Empfangsregister auf einem externen Gerät. Dann werden die Rollen der Fronten in der Zeit unterschiedlich verteilt (Abb. 10).

Zahl: 10. Gegenseitige Anordnung der Fronten in dem Fall, in dem die Quelle durch die ansteigende Flanke und der Empfänger durch die abfallende Flanke getaktet wird.

Durch diese Einbeziehung von Registern können Sie die Größe der Schlitze für Voreinstellung und Halten ausrichten. Wenn die Register von den Fronten der gleichen Richtung aus arbeiten würden, wäre der voreingestellte Durchhang aufgrund der im Vergleich zur Taktperiode geringen Ausbreitung von Signalen entlang der Plattenspuren groß und der Halte-Durchhang sehr gering.

Fig. 11 zeigt das Timing der Uhr an der Taktquelle. Um die Abbildung zu vereinfachen, habe ich den Begriff ClkTraceExt nicht angegeben. Wir gehen davon aus, dass sich die Quelle des Shreds in einem externen Gerät befindet.

Zahl: 11. Die zeitliche Position der Schlupfwinkel relativ zu den Taktfronten in dem Fall, in dem der Empfänger durch die fallende Flanke getaktet wird.

In diesem Bild max Datenankunft- Dies ist der letzte Moment, in dem Daten am Eingang des Empfängers ankommen können. Der früheste Zeitpunkt, an dem sich die Daten bereits am Eingang des Empfängers befinden sollten, ist min Data Required . Der letzte Moment, in dem noch Daten am Eingang des Empfängers vorhanden sein müssen, ist max. Erforderliche Daten . Und der früheste Moment, in dem Daten die Eingabe des Empfängers bereits verlassen können und durch die nächsten Daten ersetzt werden, wird als min Data Leaving bezeichnet .

Jetzt sollten die Formeln und ihre Begriffe klarer werden.

Verwendung der resultierenden Formeln

Wir haben Formeln für externe Verzögerungen erhalten und können eine bestimmte Anzahl von Verzögerungen berechnen, um sie in die Zeitbeschränkungsdatei einzufügen. Diese Formeln bestehen global aus zwei Arten von Begriffen - den Timing-Eigenschaften der Ports des externen Geräts und der Latenz auf den Platinenbahnen.

Portspezifikationen finden Sie normalerweise in Datenblättern unter dem Titel "Elektrische Eigenschaften / AC-Spezifikationen / Timing-Anforderungen". Manchmal werden diese Merkmale mit unterschiedlichen Namen bezeichnet, und Sie müssen klug sein, um sie zu finden. Tabellen mit Zahlen werden jedoch normalerweise von Zeitdiagrammen begleitet, mit denen Sie den gewünschten Parameter identifizieren können. Eine wichtige Nuance, die verwirrend sein kann. In Datenblättern für viele Mikroschaltungen werden Ausgangspins häufig durch die Parameter "Setup Output Time" und "Hold Output Time" beschrieben. In den Formeln dieses Artikels sollten sie wie folgt verglichen werden:tS.U.Ö=maxt∗C.Ö,tH.Ö=Mindestt∗C.Ö...

Mit Tracks ist es etwas komplizierter. Die genaue Berechnung der Latenz auf der Platine ist keine triviale Frage. Die Verzögerung hängt von der Länge, Breite, Dicke und den Winkeln der Spur, der Dicke und dem Material der Platte, dem Abstand zu verschiedenen Bodenschichten, der Nähe der Spuren zueinander und vielen anderen Faktoren ab. Der Einfluss jedes dieser Faktoren ist jedoch eher gering und bei niedrigen Grenzflächenfrequenzen von bis zu zehn Megahertz können diese Schwierigkeiten vernachlässigt werden. Eine vereinfachte Berechnung der Spurverzögerung sieht folgendermaßen aus: Die Ausbreitungsgeschwindigkeit einer Welle in der Folie wird als gleich der halben Lichtgeschwindigkeit im Vakuum angesehen. Bei der Umwandlung ergibt dies ungefähr 0,007 ns / mm. Der Fehler dieser Schätzung wird durch einen weiten Bereich von Verzögerungsschätzungen ausgeglichen. Für die maximale Verzögerung betrachten wir die spezifische Verzögerung als 0,010 ns / mm und für die minimale - 0,005 ns / mm.

Es gibt noch eine Nuance. Schaltungsingenieure versuchen beim Entwerfen von Leiterplatten, die Spuren synchroner Schnittstellen ungefähr auf die gleiche Weise zu dehnen und die gleiche Länge beizubehalten. Überprüfen Sie die Daten- und Taktspurlängen auf Ihrer Zielplatine. Höchstwahrscheinlich sind sie fast gleich und die Komponente von Ausdrücken (DataTrace - ClkTrace) kann in der Praxis als null betrachtet werden.

Wenn sich im Pfad der Daten oder des Blocks ein Verzögerungselement befindet, muss dies ebenfalls berücksichtigt werden. Dies kann ein Puffer, ein Wechselrichter, ein Pegelwandler oder eine galvanische Trennung sein. Solche Elemente können eine sehr große Verzögerung von zehn Nanosekunden verursachen, weshalb sie sehr sorgfältig behandelt werden müssen.

Fazit

In diesem Artikel haben Sie die Formeln gesehen, die die Ausführung von Zeitbeschränkungen in synchronen Schnittstellen bestimmen. Wenn Sie diese Formeln kennen, können Sie verstehen, wovon die erfolgreiche Datenübertragung abhängt und wie Sie die richtigen Grenzwerte für den Analysator berechnen. Im nächsten Artikel werde ich ein Beispiel für die Formatierung einer Zeitbeschränkungsdatei und die Verwendung des Analysators geben.