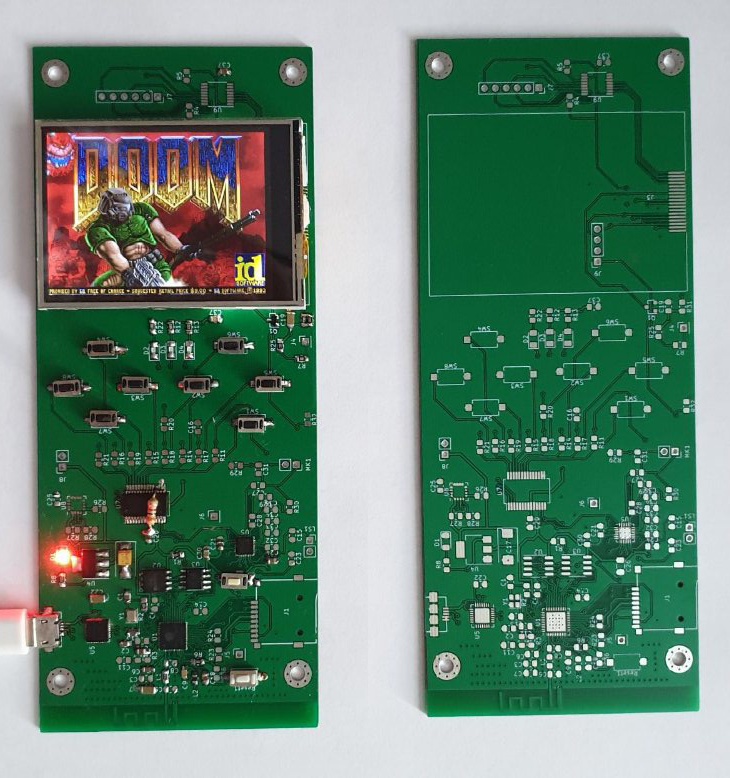

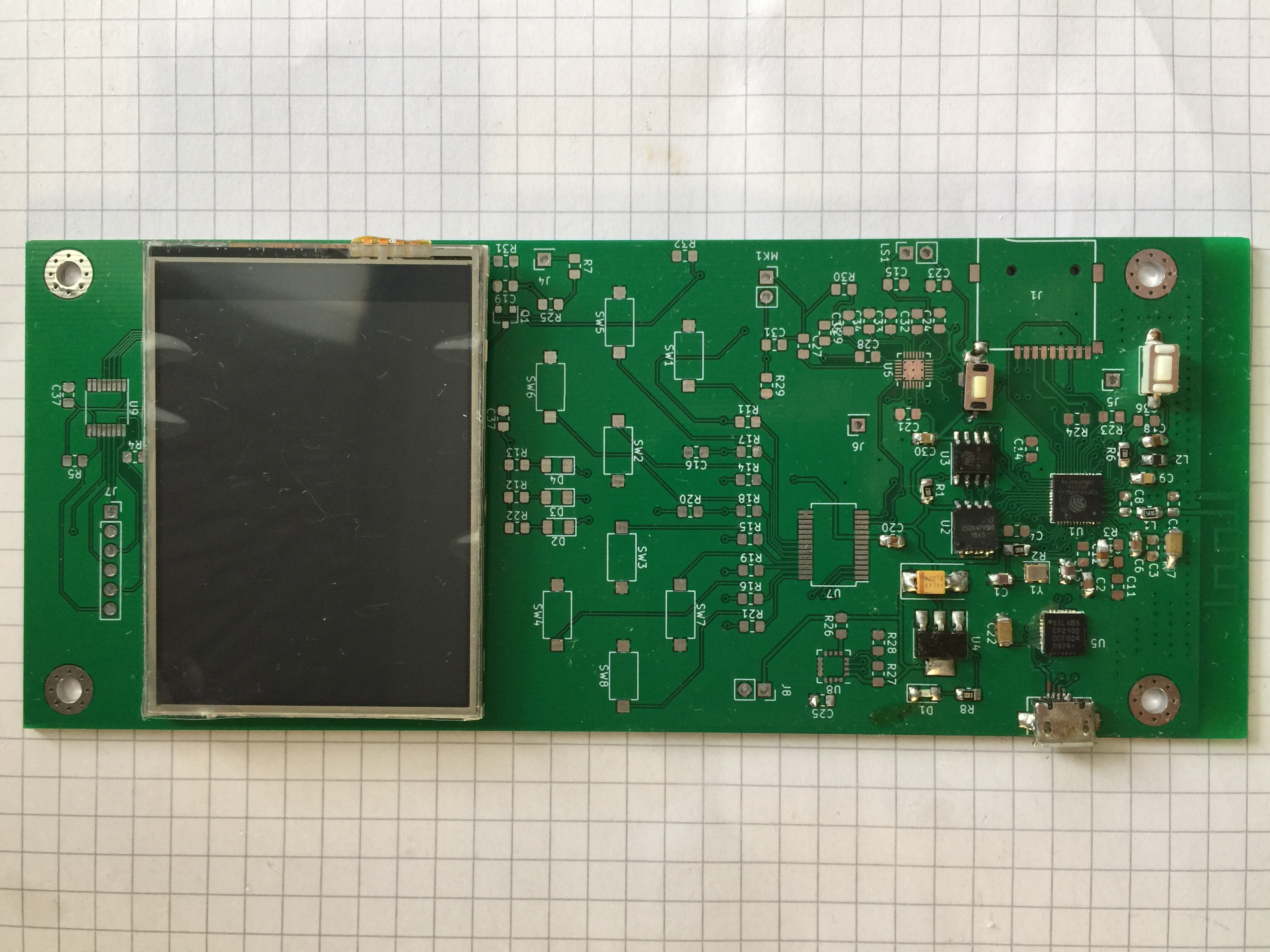

Das Hauptziel war es, den esp32d0wdq6-Chip zu entlöten. Nicht das fertige Modul selbst, sondern eine separate Mikroschaltung mit separatem Flash und PSRAM. Wie es gemacht wird und funktioniert, lesen und schauen Sie mit Video-Demos weiter

Hier können Sie über die erste Iteration des Boards lesen

Booten

Boot-Protokoll

rst:0x1 (POWERON_RESET),boot:0x13 (SPI_FAST_FLASH_BOOT)

configsip: 0, SPIWP:0xee

clk_drv:0x00,q_drv:0x00,d_drv:0x00,cs0_drv:0x00,hd_drv:0x00,wp_drv:0x00

mode:DIO, clock div:2

load:0x3fff0030,len:4

load:0x3fff0034,len:7076

load:0x40078000,len:14600

load:0x40080400,len:4160

0x40080400: _init at ??:?

entry 0x40080684

I (28) boot: ESP-IDF v4.2-dev-2243-gcf056a7d0-dirty 2nd stage bootloader

I (29) boot: compile time 18:51:57

I (30) boot: chip revision: 1

I (33) boot_comm: chip revision: 1, min. bootloader chip revision: 0

I (52) boot.esp32: SPI Speed: 40MHz

I (53) boot.esp32: SPI Mode: DIO

I (53) boot.esp32: SPI Flash Size: 8MB

I (56) boot: Enabling RNG early entropy source…

I (62) boot: Partition Table:

I (65) boot: ## Label Usage Type ST Offset Length

I (73) boot: 0 factory factory app 00 00 00010000 000e8000

I (80) boot: 1 wifidata WiFi data 01 02 000fc000 00004000

I (88) boot: 2 wad unknown 42 06 00100000 004f4000

I (95) boot: End of partition table

I (99) boot_comm: chip revision: 1, min. application chip revision: 0

I (106) esp_image: segment 0: paddr=0x00010020 vaddr=0x3f400020 size=0x38f98 (233368) map

I (216) esp_image: segment 1: paddr=0x00048fc0 vaddr=0x3ffb0000 size=0x07058 ( 28760) load

I (230) esp_image: segment 2: paddr=0x00050020 vaddr=0x400d0020 size=0x86370 (549744) map

0x400d0020: _stext at ??:?

I (468) esp_image: segment 3: paddr=0x000d6398 vaddr=0x3ffb7058 size=0x04ec4 ( 20164) load

I (478) esp_image: segment 4: paddr=0x000db264 vaddr=0x40080000 size=0x00404 ( 1028) load

0x40080000: _WindowOverflow4 at /esp/v3.3.2/esp-idf/components/freertos/xtensa/xtensa_vectors.S:1730

I (479) esp_image: segment 5: paddr=0x000db670 vaddr=0x40080404 size=0x12b7c ( 76668) load

I (538) boot: Loaded app from partition at offset 0x10000

I (538) boot: Disabling RNG early entropy source…

I (549) psram: This chip is ESP32-D0WD

I (551) spiram: Found 64MBit SPI RAM device

I (551) spiram: SPI RAM mode: flash 40m sram 40m

I (555) spiram: PSRAM initialized, cache is in low/high (2-core) mode.

I (562) cpu_start: Pro cpu up.

I (566) cpu_start: Starting app cpu, entry point is 0x4008191c

0x4008191c: start_cpu0_default at /esp/v3.3.2/esp-idf/components/esp32/cpu_start.c:466

I (0) cpu_start: App cpu up.

I (1454) spiram: SPI SRAM memory test OK

I (1462) cpu_start: Pro cpu start user code

I (1462) cpu_start: Application information:

I (1462) cpu_start: Project name: esp32_doom

I (1466) cpu_start: App version: 085f21b-dirty

I (1472) cpu_start: Compile time: Jul 26 2020 18:51:49

I (1478) cpu_start: ELF file SHA256: 9166eca39a0109f9…

I (1484) cpu_start: ESP-IDF: v4.2-dev-2243-gcf056a7d0-dirty

I (1491) heap_init: Initializing. RAM available for dynamic allocation:

I (1498) heap_init: At 3FFAE6E0 len 00001920 (6 KiB): DRAM

I (1504) heap_init: At 3FFCF628 len 000109D8 (66 KiB): DRAM

I (1511) heap_init: At 3FFE0440 len 00003AE0 (14 KiB): D/IRAM

I (1517) heap_init: At 3FFE4350 len 0001BCB0 (111 KiB): D/IRAM

I (1524) heap_init: At 40092F80 len 0000D080 (52 KiB): IRAM

I (1530) spiram: Adding pool of 4096K of external SPI memory to heap allocator

I (1539) spi_flash: detected chip: generic

I (1543) spi_flash: flash io: dio

I (1548) cpu_start: Starting scheduler on PRO CPU.

I (0) cpu_start: Starting scheduler on APP CPU.

I (1557) spiram: Reserving pool of 32K of internal memory for DMA/internal allocations

configsip: 0, SPIWP:0xee

clk_drv:0x00,q_drv:0x00,d_drv:0x00,cs0_drv:0x00,hd_drv:0x00,wp_drv:0x00

mode:DIO, clock div:2

load:0x3fff0030,len:4

load:0x3fff0034,len:7076

load:0x40078000,len:14600

load:0x40080400,len:4160

0x40080400: _init at ??:?

entry 0x40080684

I (28) boot: ESP-IDF v4.2-dev-2243-gcf056a7d0-dirty 2nd stage bootloader

I (29) boot: compile time 18:51:57

I (30) boot: chip revision: 1

I (33) boot_comm: chip revision: 1, min. bootloader chip revision: 0

I (52) boot.esp32: SPI Speed: 40MHz

I (53) boot.esp32: SPI Mode: DIO

I (53) boot.esp32: SPI Flash Size: 8MB

I (56) boot: Enabling RNG early entropy source…

I (62) boot: Partition Table:

I (65) boot: ## Label Usage Type ST Offset Length

I (73) boot: 0 factory factory app 00 00 00010000 000e8000

I (80) boot: 1 wifidata WiFi data 01 02 000fc000 00004000

I (88) boot: 2 wad unknown 42 06 00100000 004f4000

I (95) boot: End of partition table

I (99) boot_comm: chip revision: 1, min. application chip revision: 0

I (106) esp_image: segment 0: paddr=0x00010020 vaddr=0x3f400020 size=0x38f98 (233368) map

I (216) esp_image: segment 1: paddr=0x00048fc0 vaddr=0x3ffb0000 size=0x07058 ( 28760) load

I (230) esp_image: segment 2: paddr=0x00050020 vaddr=0x400d0020 size=0x86370 (549744) map

0x400d0020: _stext at ??:?

I (468) esp_image: segment 3: paddr=0x000d6398 vaddr=0x3ffb7058 size=0x04ec4 ( 20164) load

I (478) esp_image: segment 4: paddr=0x000db264 vaddr=0x40080000 size=0x00404 ( 1028) load

0x40080000: _WindowOverflow4 at /esp/v3.3.2/esp-idf/components/freertos/xtensa/xtensa_vectors.S:1730

I (479) esp_image: segment 5: paddr=0x000db670 vaddr=0x40080404 size=0x12b7c ( 76668) load

I (538) boot: Loaded app from partition at offset 0x10000

I (538) boot: Disabling RNG early entropy source…

I (549) psram: This chip is ESP32-D0WD

I (551) spiram: Found 64MBit SPI RAM device

I (551) spiram: SPI RAM mode: flash 40m sram 40m

I (555) spiram: PSRAM initialized, cache is in low/high (2-core) mode.

I (562) cpu_start: Pro cpu up.

I (566) cpu_start: Starting app cpu, entry point is 0x4008191c

0x4008191c: start_cpu0_default at /esp/v3.3.2/esp-idf/components/esp32/cpu_start.c:466

I (0) cpu_start: App cpu up.

I (1454) spiram: SPI SRAM memory test OK

I (1462) cpu_start: Pro cpu start user code

I (1462) cpu_start: Application information:

I (1462) cpu_start: Project name: esp32_doom

I (1466) cpu_start: App version: 085f21b-dirty

I (1472) cpu_start: Compile time: Jul 26 2020 18:51:49

I (1478) cpu_start: ELF file SHA256: 9166eca39a0109f9…

I (1484) cpu_start: ESP-IDF: v4.2-dev-2243-gcf056a7d0-dirty

I (1491) heap_init: Initializing. RAM available for dynamic allocation:

I (1498) heap_init: At 3FFAE6E0 len 00001920 (6 KiB): DRAM

I (1504) heap_init: At 3FFCF628 len 000109D8 (66 KiB): DRAM

I (1511) heap_init: At 3FFE0440 len 00003AE0 (14 KiB): D/IRAM

I (1517) heap_init: At 3FFE4350 len 0001BCB0 (111 KiB): D/IRAM

I (1524) heap_init: At 40092F80 len 0000D080 (52 KiB): IRAM

I (1530) spiram: Adding pool of 4096K of external SPI memory to heap allocator

I (1539) spi_flash: detected chip: generic

I (1543) spi_flash: flash io: dio

I (1548) cpu_start: Starting scheduler on PRO CPU.

I (0) cpu_start: Starting scheduler on APP CPU.

I (1557) spiram: Reserving pool of 32K of internal memory for DMA/internal allocations

KiCad PCB

In KiCad schien mir alles einfacher zu sein. Für meinen Geschmack natürlich. Etwas anders als Eagle Autodesk. Das Hauptvorteil ist, dass die Höhe der Gebühren unbegrenzt ist, wenn Sie keine Lizenz bezahlen möchten. Ich möchte Sie daran erinnern, dass Eagle eine Größenbeschränkung von 100 x 80 mm für die kostenlose Entwicklung hat. Wenn die Gebühr höher ist, müssen Sie eine jährliche Lizenz bezahlen. Meiner Meinung nach ist auch die Anzahl der Schichten begrenzt

Ich konnte 3D View in Eagle nicht sehen. Eagle Fusion 360 muss installiert werden. In Kicad ist dies ein separater Menüpunkt. Obwohl ich dort vielleicht nicht gesucht habe. Im Allgemeinen können wir sagen, vollständig auf KiCad

umgestellt. Hat alles in Module unterteilt und auf der Hauptseite belassen, was direkt mit ESP32 zusammenhängt. Der Chip selbst und der Speicher

Fehler

Ich zeichnete die Tafel in Pausen. Infolgedessen habe ich vergessen, GPIO0 auszugeben. Ich habe es als MCCLK zum externen DAC gebracht, aber ich habe vergessen, es in die Schaltfläche für den Download-Modus zu bringen. Ich musste den Lack von der Lötschiene für die Tastenausgabe abreißen. Außerdem wurde der Widerstand in der Quarzschaltung auf XTAL_N eingestellt, und im Handbuch ist XTAL_P erforderlich. Ich habe einen Widerstand von mehreren Ohm aufgehängt, aber es war möglich, einen Jumper zu werfen. Die

Adress- und Reset-Widerstände für den MCP23017 ließen sich nicht scheiden. Der Chip kann mit drei Pins auf die I2C-Adresse eingestellt werden. 0x20h wenn alle drei Stifte am Boden liegen. Alles, weil ich FootPrint nicht angegeben habe, habe

ich den Fehler nicht beachtet

Fehler: R10 kann nicht hinzugefügt werden (kein Footprint zugewiesen).

Fehler: R9 kann nicht hinzugefügt werden (kein Footprint zugewiesen)

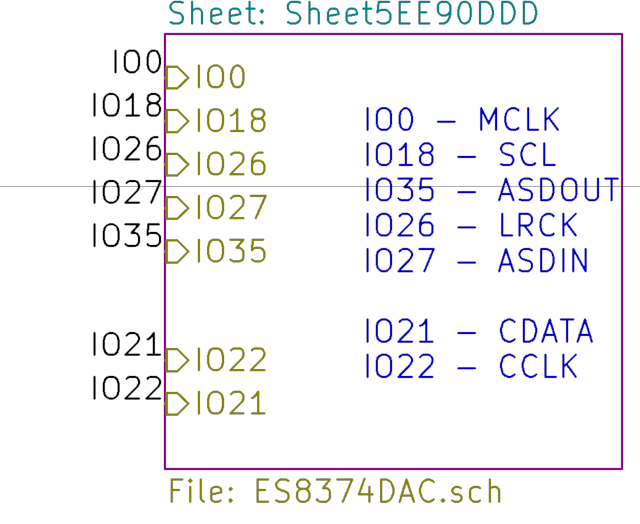

Verwirrtes i2C für ES8374. Manchmal passiert es. Grundsätzlich können Sie die Schaltstifte 21 -> 22 und 22 -> 21 verwenden. Oder schneiden Sie die Schienen ab und kratzen Sie den Lack ab, wie wir es normalerweise mit TX RX Uart getan haben (trauriges Lächeln).

Überraschenderweise startete die Platine nach dem Löten von ESP32 und FLASH ohne Probleme. Aber nachdem ich SPRAM gesetzt hatte, bekam ich einen endlosen Neustart. Es stellte sich als banaler Mangel an Nahrung heraus. Ich würde suchen, wenn der ESP32 nicht gelötet ist!

Multiplexer MCP23017

Bereitstellung der Möglichkeit einer alternativen Abfrage von Tasten sowohl über den Multiplexer MCP23017 als auch über den DAC. Auf einem Widerstandsteiler. Wenn es nicht möglich ist, einen Multiplexer zu installieren, können Sie den internen ADC verwenden. Anhand des Spannungspegels am GPIO34-Eingang können Sie einen Tastendruck erkennen. Der Nachteil ist, dass es nicht möglich ist, mehrere Schaltflächen gleichzeitig abzufragen. Außerdem wird keine zusätzliche Mikroschaltung benötigt. Nur wenige Widerstände Der

Multiplexer verfügt über 2 Ports mit 8 Pins. In unserem Fall kann ein Port als Ausgang konfiguriert und LEDs daran aufgehängt werden. Ich wollte für ein Blinken sorgen, wenn die Lebensdauer weniger als 20% beträgt oder die Patronen leer sind. Dann können Sie ohne das Panel spielen. Es stellte sich heraus, dass es realisiert wurde. Eine grüne LED bleibt erhalten. Wenn sich keine Feinde im Raum oder in Sichtweite befinden, können Sie beleuchten

Thread der Gesundheits- und Munitionsanzeige

void ledTask(void *arg){

while(1){

p = &players[cur_player];

if (p->mo != NULL && p->mo->health < 20) {

mcp23x17_set_level(&dev, 9, on);

} else {

mcp23x17_set_level(&dev, 9, true);

}

if(p->ammo[weaponinfo[p->readyweapon].ammo] < 5){

mcp23x17_set_level(&dev, 10, on);

} else {

mcp23x17_set_level(&dev, 10, true);

}

printf("p->ammo[am_clip] = %d\n", p->ammo[weaponinfo[p->readyweapon].ammo]);

if (p->mo != NULL) {

printf("p->mo->health = %d \n", p->mo->health);

}

printf("Ammo N = %d\n", weaponinfo[p->readyweapon].ammo);

on = !on;

vTaskDelay(1000/portTICK_PERIOD_MS);

}

}

ES8374 Audio-Chip

Für den Sound habe ich ES8374 als DAC und ADC verwendet. Die Mikroschaltung enthält einen eingebauten Niederfrequenzverstärker ~ 1,25 Watt. Es wird sofort vom Espressif Audio Development Framework unterstützt . Im kleinen QFN-28-Paket erhalten wir Mono DAC, ADC für Mikrofon und ULF mit SDK-Unterstützung. Was wird für ein solches Gerät benötigt ? Starten Sie

BT Speaker aus dem Beispiel Pipeline_Bt_Sink.

Ich habe die Karte lyrat_v4_3 in den Einstellungen verwendet. Codec an AUDIO_CODEC_ES8374_DEFAULT_HANDLE behoben.

Konfigurierte GPIO-Ports

esp_err_t get_i2s_pins(i2s_port_t port, i2s_pin_config_t *i2s_config)

{

AUDIO_NULL_CHECK(TAG, i2s_config, return ESP_FAIL);

if (port == I2S_NUM_0 || port == I2S_NUM_1) {

i2s_config->bck_io_num = GPIO_NUM_18;

i2s_config->ws_io_num = GPIO_NUM_26;

i2s_config->data_out_num = GPIO_NUM_27;

i2s_config->data_in_num = GPIO_NUM_35;

} else {

memset(i2s_config, -1, sizeof(i2s_pin_config_t));

ESP_LOGE(TAG, "i2s port %d is not supported", port);

return ESP_FAIL;

}

return ESP_OK;

}

Und warf die Initialisierung von audio_board_key_init und audio_board_led_init aus. Durch das richtige müssen Sie Ihr benutzerdefiniertes Board bestimmen

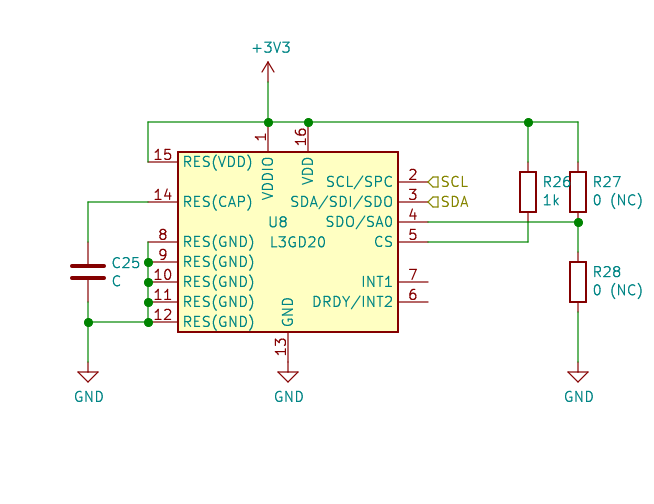

Gyroskop L3GD20

Ich habe mich für das Gyroskop L3GD20 entschieden. Eine interessante Funktion ist, dass es als SPI- oder I2C-Gerät angeschlossen werden kann. R27, R28 bei Verbindung über I2C die Adresse einstellen

// L3GD20H-AdressenAuf GitHub gibt es eine Bibliothek l3gd20h-esp-idf

#define L3GD20H_I2C_ADDRESS_1 0x6a // SDO-Pin ist niedrig

#define L3GD20H_I2C_ADDRESS_2 0x6b // SDO-Pin ist hoch

. Wir haben also 3 Geräte auf I2C. ADC-DAC ES8374-Steuerung, Tasten am MCP23017 und L3GD20 selbst. Startete alle drei

i2cdetect

i2c-tools> i2cdetect

0 1 2 3 4 5 6 7 8 9 a b c d e f

00: — -- — -- — -- — -- — -- — -- — -- — --

10: 10 — -- — -- — -- — -- — -- — -- — -- —

20: — -- — -- 24 — -- — -- — -- — -- — -- —

30: — -- — -- — -- — -- — -- — -- — -- — --

40: — -- — -- — -- — -- — -- — -- — -- — --

50: — -- — -- — -- — -- — -- — -- — -- — --

60: — -- — -- — -- — -- — -- 6a — -- — -- —

70: — -- — -- — -- — -- — -- — -- — -- — --

0 1 2 3 4 5 6 7 8 9 a b c d e f

00: — -- — -- — -- — -- — -- — -- — -- — --

10: 10 — -- — -- — -- — -- — -- — -- — -- —

20: — -- — -- 24 — -- — -- — -- — -- — -- —

30: — -- — -- — -- — -- — -- — -- — -- — --

40: — -- — -- — -- — -- — -- — -- — -- — --

50: — -- — -- — -- — -- — -- — -- — -- — --

60: — -- — -- — -- — -- — -- 6a — -- — -- —

70: — -- — -- — -- — -- — -- — -- — -- — --

Aus irgendeinem Grund gibt L3GD20 keine Koordinaten an. WHO_AM_I antwortet korrekt mit 0xd4. Die Winkel ändern sich nicht. Ich habe keinen Kondensator C1 - 10nF, ich habe versucht zu setzen, welcher die nächsten 100nF gefunden hat. Ich dachte, auch wenn er gelogen hat, aber es scheint, dass der interne Konverter nicht startet. Und das ist wichtig

i2cdump

i2c-tools> i2cdump -c 0x6a

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: b6 5e 81 fc 05 50 31 83 c4 f9 85 d0 48 c6 00 d4 ?^???P1?????H?.?

10: 1a 15 16 ea c0 b9 4f 72 07 d8 a1 21 a1 00 14 02 ??????Or???!?.??

20: 07 00 00 80 00 00 0c 00 1a 00 13 00 16 00 00 20 ?..?..?.?.?.?..

30: 00 00 00 00 00 00 00 00 00 05 00 00 00 00 00 00 .........?..

40: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00…

50: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00…

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00…

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00…

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: b6 5e 81 fc 05 50 31 83 c4 f9 85 d0 48 c6 00 d4 ?^???P1?????H?.?

10: 1a 15 16 ea c0 b9 4f 72 07 d8 a1 21 a1 00 14 02 ??????Or???!?.??

20: 07 00 00 80 00 00 0c 00 1a 00 13 00 16 00 00 20 ?..?..?.?.?.?..

30: 00 00 00 00 00 00 00 00 00 05 00 00 00 00 00 00 .........?..

40: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00…

50: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00…

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00…

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00…

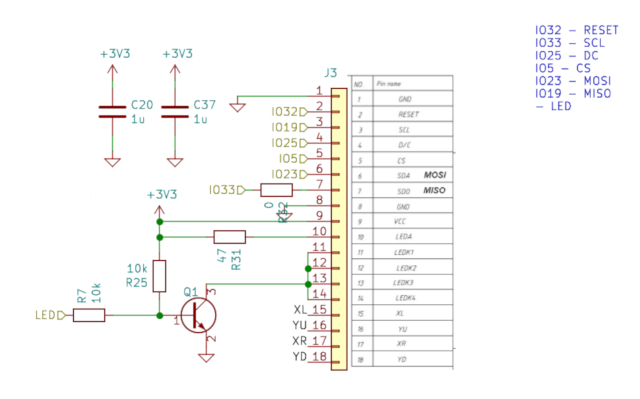

Anzeige 18 Pin ILI9341

Berechnete den Hintergrundbeleuchtungsstrom wie folgt. Benötigt 90mA. Da der Abfall über dem offenen Transistor ~ 0,7 V beträgt, beträgt die Stromversorgung für die LEDs mit Hintergrundbeleuchtung 3,3 V - 0,7 V = 2,6 V. Und nach dem Ohmschen Gesetz 2,6 V / 0,090 A = 28,8 Ohm. Geliefert 47 Ohm. Es stellte sich ein wenig dunkel heraus. Der Widerstand muss reduziert werden.

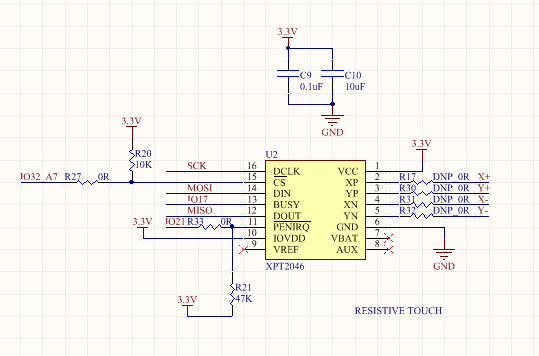

Außerdem wurde der Touch XPT2046TS getrennt. Parallel zum Display hingen SPI-Pins. XPT_CS wird auf einem separaten Pin angezeigt. Es besteht ein Zweifel, dass es funktionieren wird. Wenn das Display nicht gestartet worden wäre, hätte ich Experimente durchgeführt. Für die Konsole wird es nicht besonders benötigt. Aus dem Beispiel genommen

Demos

LVGL-Demo gestartet. In den Beispieleinstellungen habe ich versucht, 40 MHz für den SPI-Bus einzustellen. Das Beispiel hat etwas schneller funktioniert als das Video

Aber Doom startete und arbeitete nur bei 32 MHz stabil. Obwohl 26MHz für ILI9341 bereits als Übertaktung gilt

spi_device_interface_config_t devcfg={

.clock_speed_hz=26000000, //Clock out at 26 MHz. Yes, that's heavily overclocked.

.mode=0, //SPI mode 0

.spics_io_num=PIN_NUM_CS, //CS pin

.queue_size=NO_SIM_TRANS, //We want to be able to queue this many transfers

.pre_cb=ili_spi_pre_transfer_callback, //Specify pre-transfer callback to handle D/C line

};

Fazit

ESP32-E / A-Ports reichen nicht immer aus, um das Maximum zu erreichen. In dieser Hinsicht sieht STM32 attraktiver aus. Es verfügt jedoch nicht über eine integrierte Wi-Fi-Unterstützung. Zusammenfassend

kann festgestellt werden, dass auf dem Gerät der Nintendo-Emulator ESP32-NESEMU und der Nintendo Entertainment System-Emulator für den ESP32 ausgeführt werden können.

Ich habe Game Console bei Ali bestellt. Es wird interessant sein zu sehen, was drin ist. Möglicherweise auch ESP32

Ich freue mich auf Diskussionen und Ratschläge in den Kommentaren.